Table 8: legend – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 27

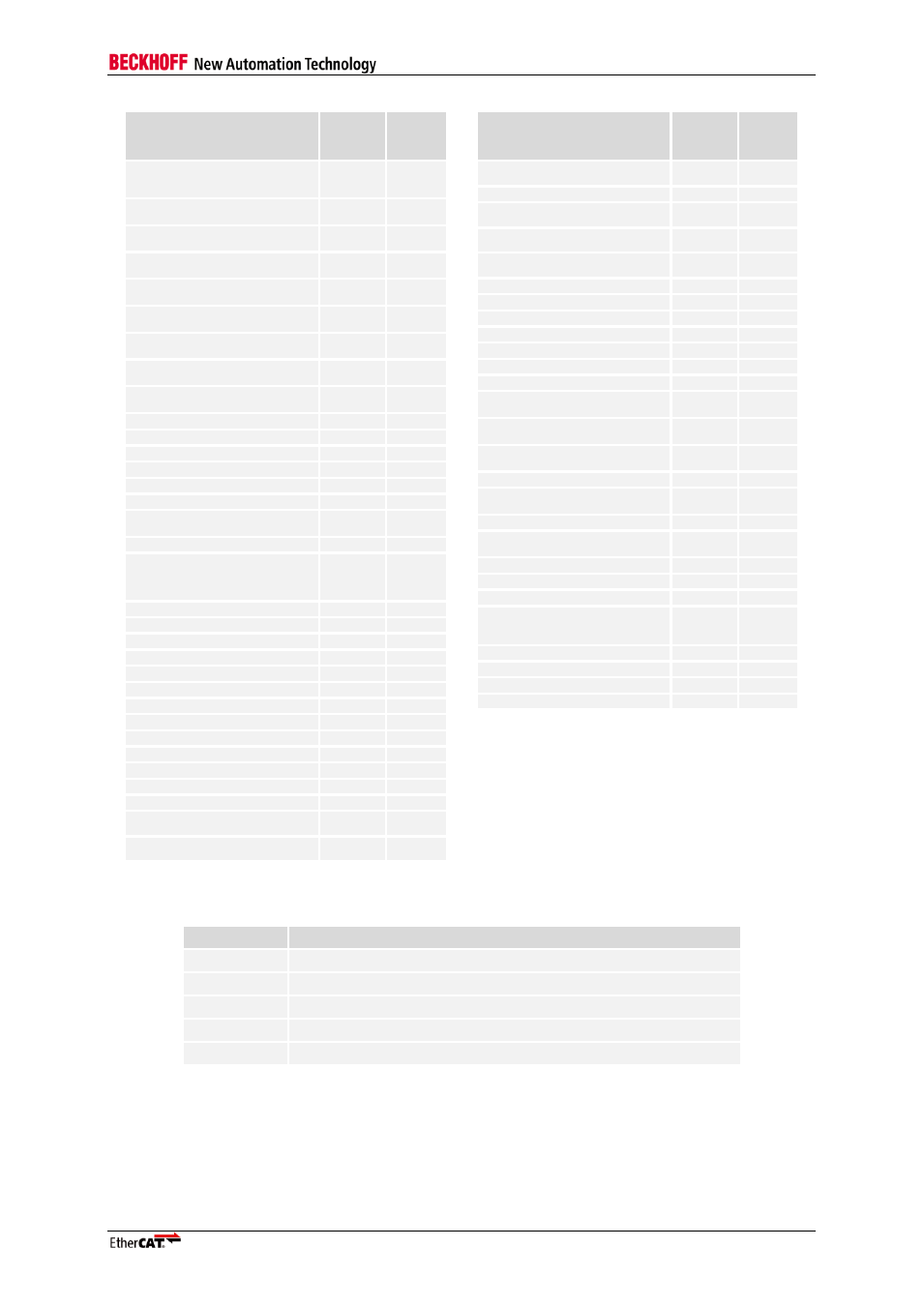

Features and Registers

Slave Controller

– IP Core for Xilinx FPGAs

III-15

Feature

IP Core

Xilinx

®

V3.00k

IP Core

Xilinx

®

V3.00c-

3.00j

Propagation delay measurement

with traffic (BWR/FPWR 0x900

detected at each port)

x

x

LatchSignal state in Latch Status

register (0x09AE:0x09AF)

x

x

SyncSignal Auto-Activation

(0x0981.3)

x

x

SyncSignal 32 or 64 bit Start Time

(0x0981.4)

x

x

SyncSignal Late Activation

(0x0981[6:5])

x

x

SyncSignal debug pulse

(0x0981.7)

x

x

SyncSignal Activation State

0x0984)

x

x

Reset filters after writing filter

depth

x

x

ESC Specific Registers

(0x0E00:0x0EFF)

Product and Vendor ID

x

x

POR Values

-

-

FPGA Update (online)

-

-

Process RAM and User RAM

Process RAM (0x1000 ff.) [Kbyte]

0-60

0-60

User RAM (0x0F80:0x0FFF)

x

x

Extended ESC Feature

Availability in User RAM

x

x

Additional EEPROMs

1-2

1-2

SII EEPROM (I²C)

c

(EEPROM

of µC used)

c

(EEPROM

of µC

used)

FPGA configuration EEPROM

x

x

LED Signals

RUN LED

c

c

RUN LED override

c

c

Link/Activity(x) LED per port

x

x

PERR(x) LED per port

-

-

Device ERR LED

c

c

STATE_RUN LED

c

c

Optional LED states

RUN LED: Bootstrap

x

x

RUN LED: Booting

c

c

RUN LED: Device identification

c

c

RUN LED: loading SII EEPROM

c

c

Error LED: SII EEPROM loading

error

c

c

Error LED: Invalid hardware

configuration

-

-

Feature

IP Core

Xilinx

®

V3.00k

IP Core

Xilinx

®

V3.00c-

3.00j

Error LED: Process data

watchdog timeout

c

c

Error LED: PDI watchdog timeout

c

c

Link/Activity: local auto-

negotiation error

-

-

Link/Activity: remote auto-

negotiation error

-

-

Link/Activity: unknown PHY auto-

negotiation error

-

-

LED test

c

c

Clock supply

Crystal

-

-

Crystal oscillator

x

x

TX_CLK from PHY

x

x

25ppm clock source accuracy

x

x

Internal PLL

User logic

User logic

Power Supply Voltages

FPGA dep.

FPGA

dep.

I/O Voltage

FPGA dep.

FPGA

dep.

Core Voltage

FPGA dep.

FPGA

dep.

Internal LDOs

-

-

Package

FPGA dep.

FPGA

dep.

Original Release date

1/2015

5/2013

Configuration and Pinout calculator

(XLS)

-

-

Register Configuration

individual

individual

Complete IP Core evaluation

x

x

License device required

-

-

Example designs/

pre-synthesized time-limited evaluation

core included

3/3

4/3

LX150T Digital I/O

x/x

x/x

LX150T AXI

x/x

x/x

ZC702 AXI (PlanAhead)

-

x/x

ZC702 AXI (Vivado)

x/x

x/-

Table 8: Legend

Symbol

Description

x

available

-

not available

c

configurable

User logic

Functionality can be added by user logic inside the FPGA

red

Feature changed in this version