8 ip core signals, 1 general signals, Ip core signals – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 71: General signals, Table 18: general signals

Advertising

IP Core Signals

Slave Controller

– IP Core for Xilinx FPGAs

III-59

8

IP Core Signals

The available signals depend on the IP Core configuration.

8.1

General Signals

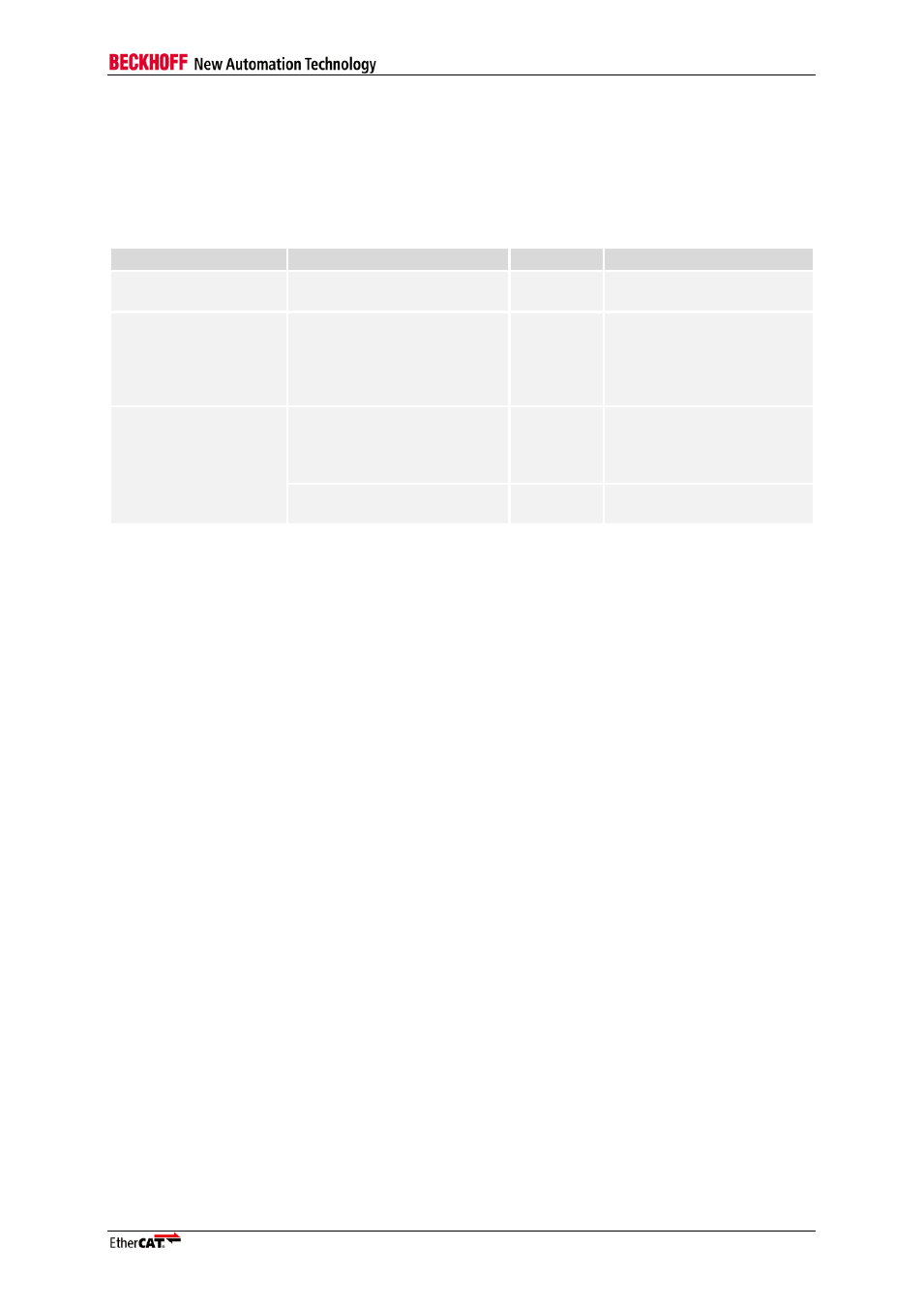

Table 18: General Signals

Condition

Name

Direction

Description

nRESET

INPUT

Resets all registers of the

IP Core, active low

Reset slave by

ECAT/PDI

RESET_OUT

OUTPUT

Reset by ECAT (reset

register 0x0040), active

high. RESET_OUT has to

trigger nRESET, which

clears RESET_OUT.

CLK25

INPUT

25 MHz clock signal from

PLL (rising edge

synchronous with rising

edge of CLK100)

CLK100

INPUT

100 MHz clock signal from

PLL

Advertising