6 axi4 / axi4 lite on-chip bus, Axi4 / axi4 lite on-chip bus, Table 34: axi4 / axi4 lite pdi – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 88

IP Core Signals

III-76

Slave Controller

– IP Core for Xilinx FPGAs

8.6.6

AXI4 / AXI4 LITE On-Chip Bus

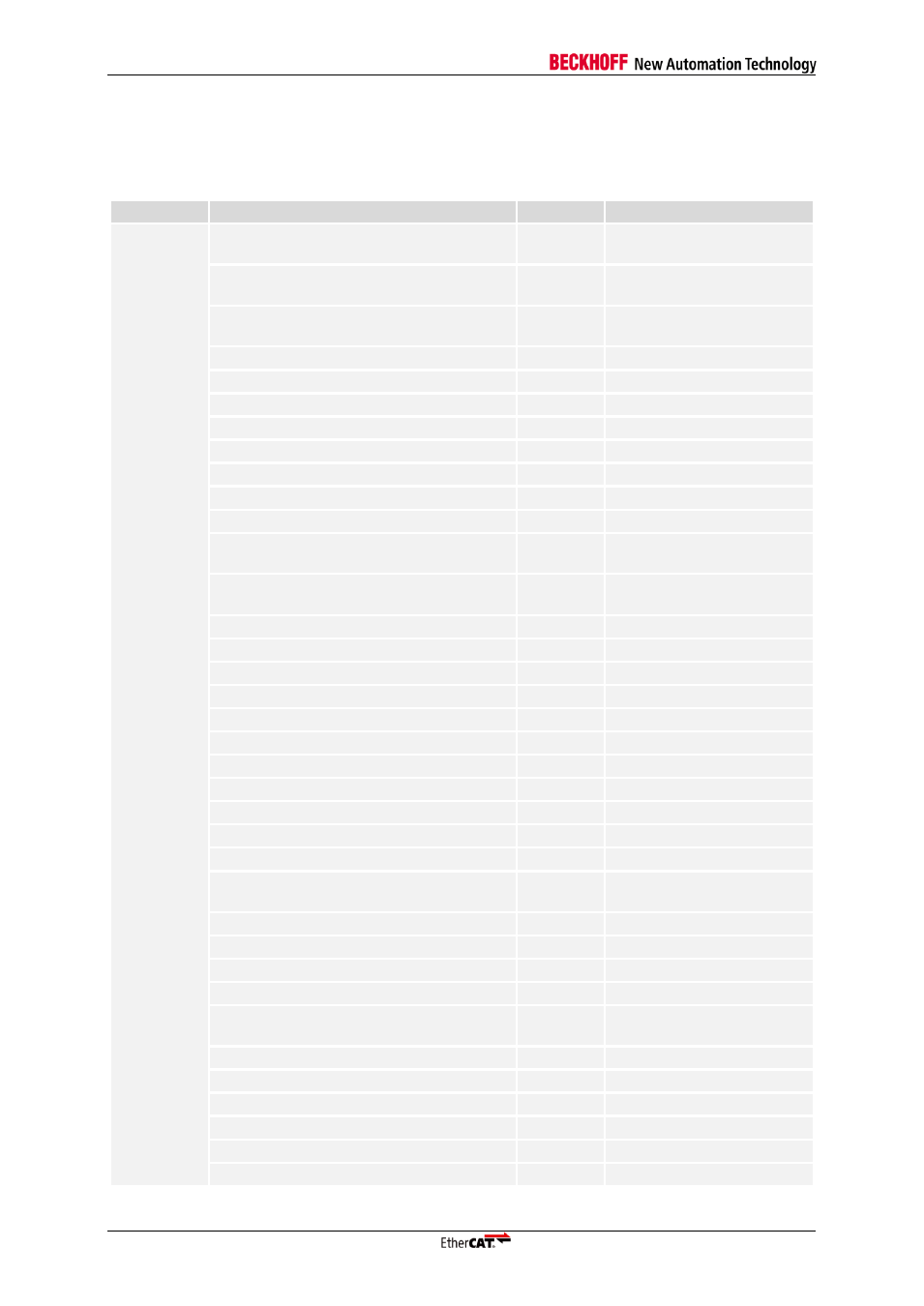

Table 34 lists the signals used with the AXI4 and AXI4 LITE PDI.

Table 34: AXI4 / AXI4 LITE PDI

Condition

Name

Direction

Description

AXI4

or

AXI4 LITE

C_S_AXI_DATA_WIDTH

GENERIC AXI data bus width

(8/16/32/64 bit)

C_S_AXI_ACLK_FREQ_HZ

GENERIC AXI bus clock frequency in

Hz (>= 25,000)

C_S_AXI_ADDR_WIDTH

GENERIC AXI address width (>= 16

bit, only 16 bit are used)

C_S_AXI_ID_WIDTH

GENERIC AXI ID width

PDI_AXI_ACLK

INPUT

AXI bus clock

PDI_AXI_AWADDR[15:0]

INPUT

Write address

PDI_AXI_AWPROT[2:0]

INPUT

Write protection type

PDI_AXI_AWREGION[3:0]

INPUT

Write region identifier

PDI_AXI_AWQOS[3:0]

INPUT

Write QoS identifier

PDI_AXI_AWVALID

INPUT

Write address valid

PDI_AXI_AWREADY

OUTPUT

Write address ready

PDI_AXI_WDATA

[PDI_EXT_BUS_WIDTH-1:0]

INPUT

Write data

PDI_AXI_WSTRB

[PDI_EXT_BUS_WIDTH/8-1:0]

INPUT

Write data byte enable

PDI_AXI_WVALID

INPUT

Write data valid

PDI_AXI_WREADY

OUTPUT

Write data ready

PDI_AXI_BRESP[1:0]

OUTPUT

Write response

PDI_AXI_BVALID

OUTPUT

Write response valid

PDI_AXI_BREADY

INPUT

Write response ready

PDI_AXI_ARADDR[15:0]

INPUT

Read address

PDI_AXI_ARPROT[2:0]

INPUT

Read protection type

PDI_AXI_ARREGION[3:0]

INPUT

Read region identifier

PDI_AXI_ARQOS[3:0]

INPUT

Read QoS identifier

PDI_AXI_ARVALID

INPUT

Read address valid

PDI_AXI_ARREADY

OUTPUT

Read address ready

PDI_AXI_RDATA

[PDI_EXT_BUS_WIDTH-1:0]

OUTPUT

Read data

PDI_AXI_RRESP[1:0]

OUTPUT

Read response

PDI_AXI_RVALID

OUTPUT

Read data valid

PDI_AXI_RREADY

INPUT

Read data ready

PDI_AXI_IRQ_MAIN

OUTPUT

Interrupt

PDI_AXI_AWID

[PDI_BUS_ID_WIDTH-1:0]

INPUT

Write address ID

PDI_AXI_AWLEN[7:0]

INPUT

Write length

PDI_AXI_AWSIZE[2:0]

INPUT

Write size

PDI_AXI_AWBURST[1:0]

INPUT

Write burst type

PDI_AXI_AWLOCK

INPUT

Write lock

PDI_AXI_AWCACHE[3:0]

INPUT

Write cache type

PDI_AXI_WLAST

INPUT

Write data last