5 ip core configuration, Ip core configuration – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 46

IP Core Configuration

III-34

Slave Controller

– IP Core for Xilinx FPGAs

5

IP Core Configuration

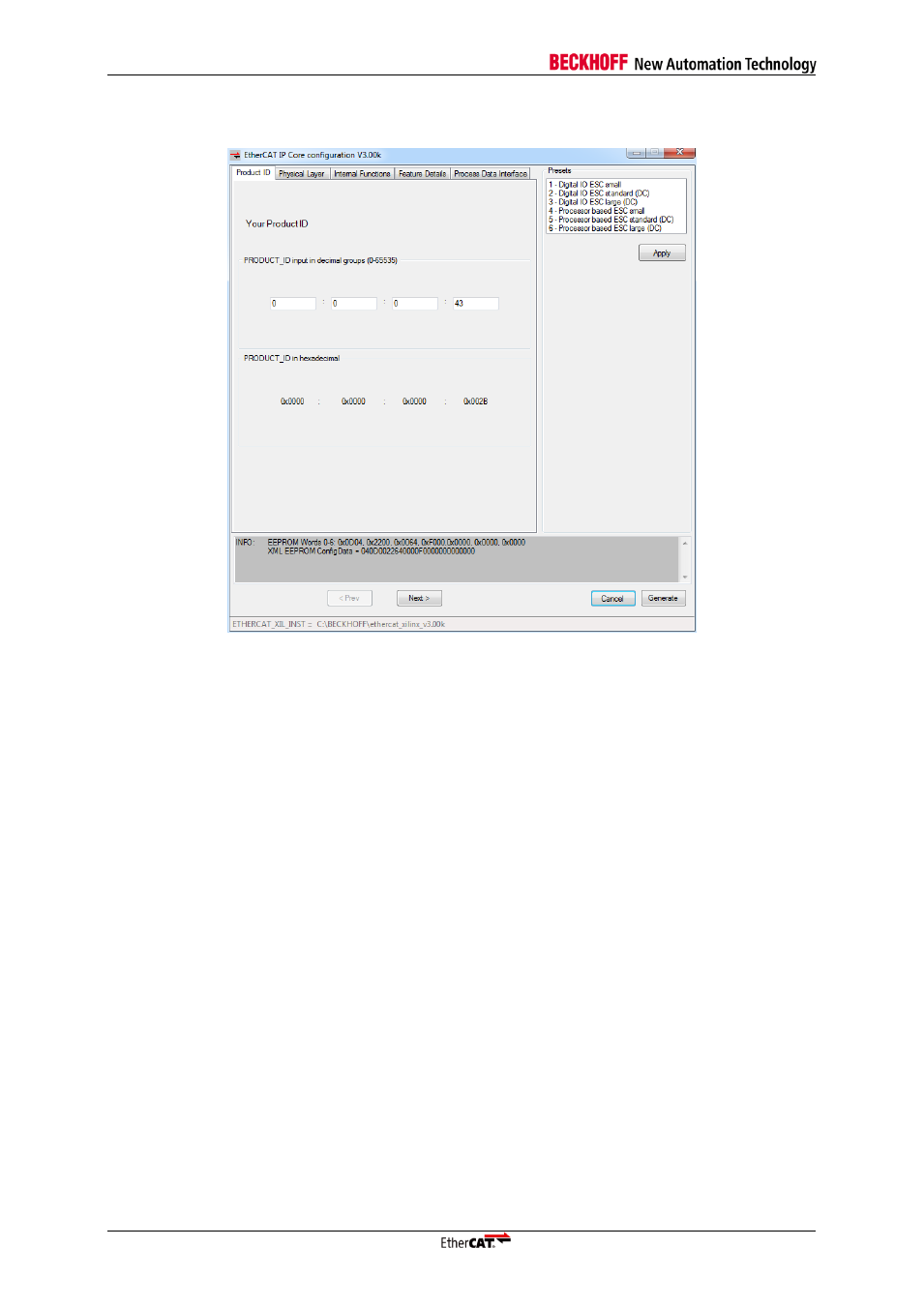

Figure 12: EtherCAT IP Core Configuration Interface

Parameters pane (left)

The configuration options for the EtherCAT IP Core are available in the IP Core parameters pane on

the left side.

Presets pane (right)

Depending on the IP Core functionality that should be implemented and the available resources (LCs)

in the FPGA, the internal features can be chosen. Several common feature presets are available.

Based upon these presets, individual functions can be enabled/disabled in the parameter pane.

Message pane (bottom)

In the lower box additional information like warnings, errors, and EEPROM configuration

recommendations are displayed.

ETHERCAT_XIL_INST (status line)

The status line displays the current ETHERCAT_XIL_INST environment variable, which points to the

EtherCAT IP Core installation directory with the required source files.