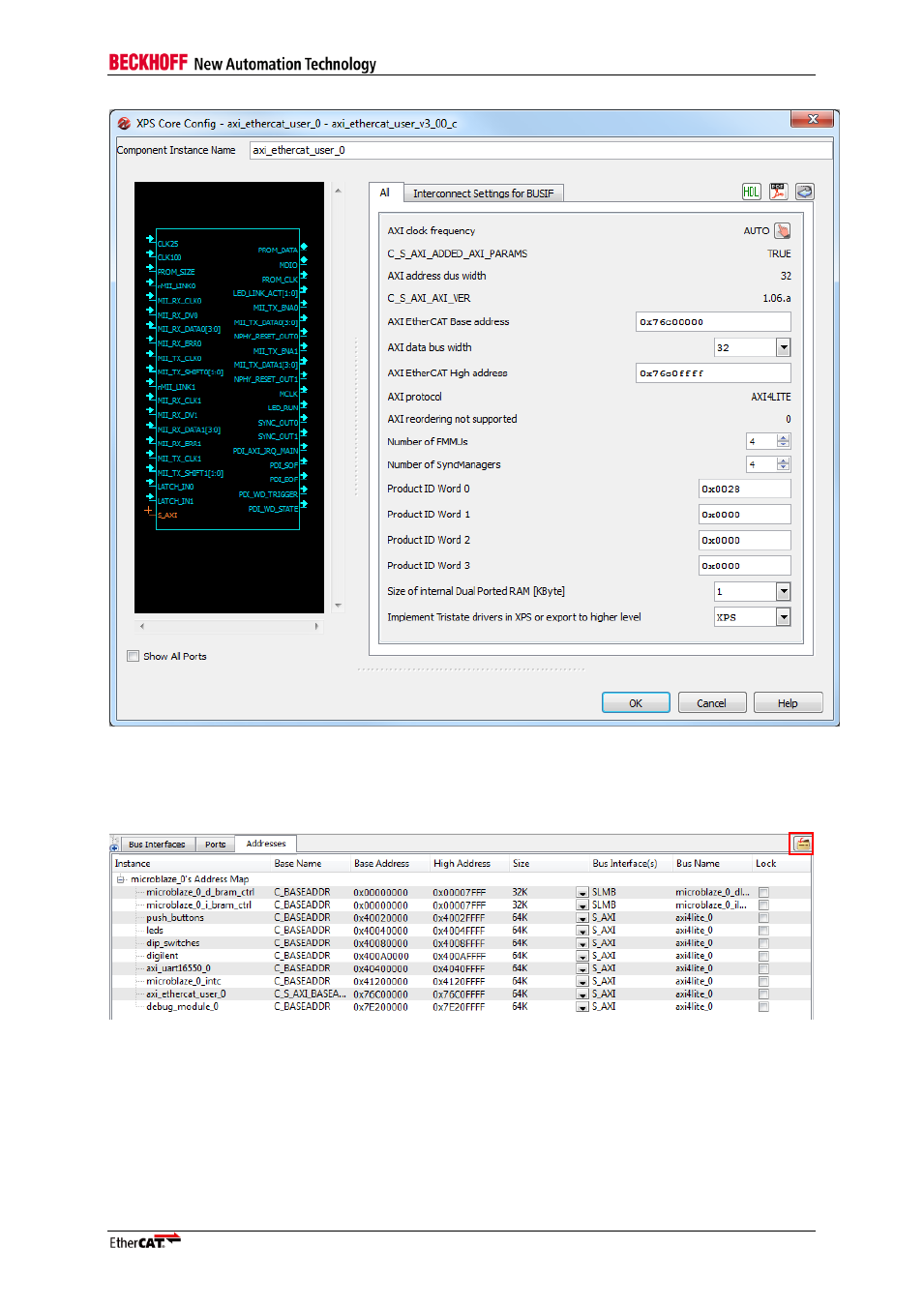

Figure 9: edk, Configuration dialog, Figure 10: edk – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 43: System assembly view, addresses tab

Advertising

IP Core Usage

Slave Controller

– IP Core for Xilinx FPGAs

III-31

Figure 9: EDK

– Configuration Dialog

10. Assign addresses to the EtherCAT IP Core. The tab "Addresses" in the "System Assembly View"

shows the internal addresses of the IP Cores. Press the Generate Addresses button to

automatically assign addresses.

Figure 10: EDK

– System Assembly View, Addresses tab

Note:

If you have added a new IP Core, you can generate or set the internal addresses. The EtherCAT

IP core needs at least 64 Kbyte address space. Larger sizes will result in less address decoding

logic.

Advertising