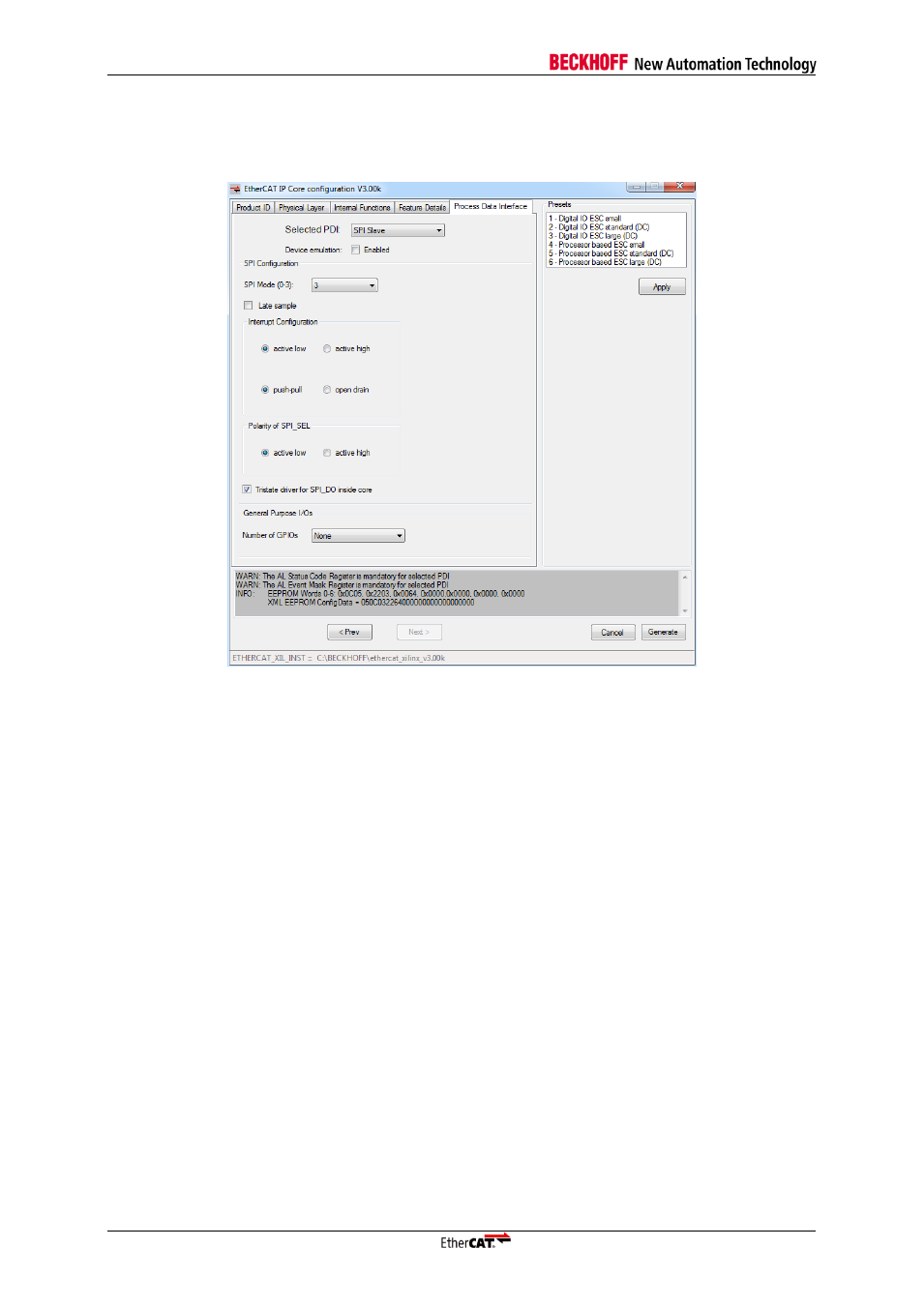

4 spi configuration, Figure 21: register pdi, Spi configuration – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 58

IP Core Configuration

III-46

Slave Controller

– IP Core for Xilinx FPGAs

5.1.5.4

SPI Configuration

The SPI interface is a serial slave interface for µControllers.

Figure 21: Register PDI

– SPI Configuration

Device emulation

Enable Device emulation (0x0141[0]=1). This feature should be disabled in most use cases.

SPI Mode

The SPI mode determines the SPI timing. Refer to SPI PDI description for details. Mode 3 is

recommended for slave sample code.

Late Sample

The Late Sample configuration determines the SPI timing. Refer to SPI PDI description for details. It is

recommended to leave this unchecked for slave sample code.

Interrupt Configuration

SPI_IRQ output driver configuration.

Polarity of SPI_SEL

SPI_SEL signal polarity.

Tristate driver for SPI_DO inside core

Include tri-state driver for SPI Data Out. With tri-state driver, SPI_DO is either driven actively or high

impedance output.