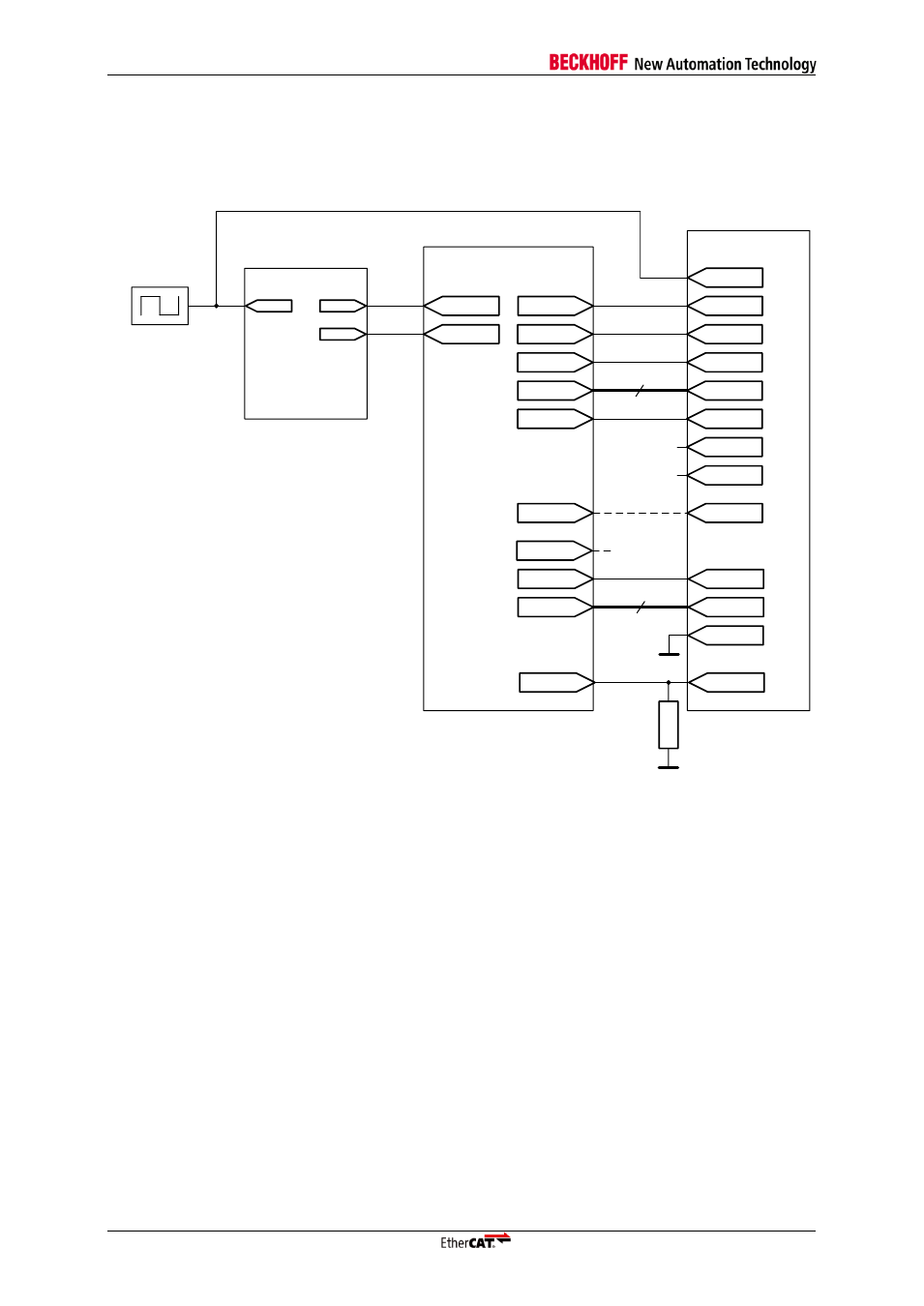

4 mii example schematic, Mii example schematic, Figure 32: mii example schematic – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 96: Ethercat ip core ethernet phy, Optional, 25 mhz

Advertising

Ethernet Interface

III-84

Slave Controller

– IP Core for Xilinx FPGAs

9.2.4

MII example schematic

Refer to chapter 8.5.1 for more information on special markings (!). Take care of proper compensation

of the TX_CLK phase shift.

EtherCAT IP Core

Ethernet PHY

MII_RX_DV

MII_RX_DATA[3:0]

MII_RX_ERR

MII_TX_ENA

MII_TX_DATA[3:0]

MII_RX_CLK

RX_DV

RXD[3:0]

RX_ER

TX_EN

TXD[3:0]

RX_CLK

TX_CLK

CLK25

CRS

TX_ER

COL

nMII_LINK

LINK_STATUS

!

!

! optional

CLK25

PLL

CLK_IN

CLK25

CLK100

CLK100

25 MHz

MII_TX_CLK

! optional

MII_TX_SHIFT[1:0]

00/01/10/11

NPHY_RESET_OUT

NRESET

4

K

7

Figure 32: MII example schematic

Advertising