Altera RapidIO II MegaCore Function User Manual

Page 106

4–64

Chapter 4: Functional Description

Logical Layer Interfaces

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

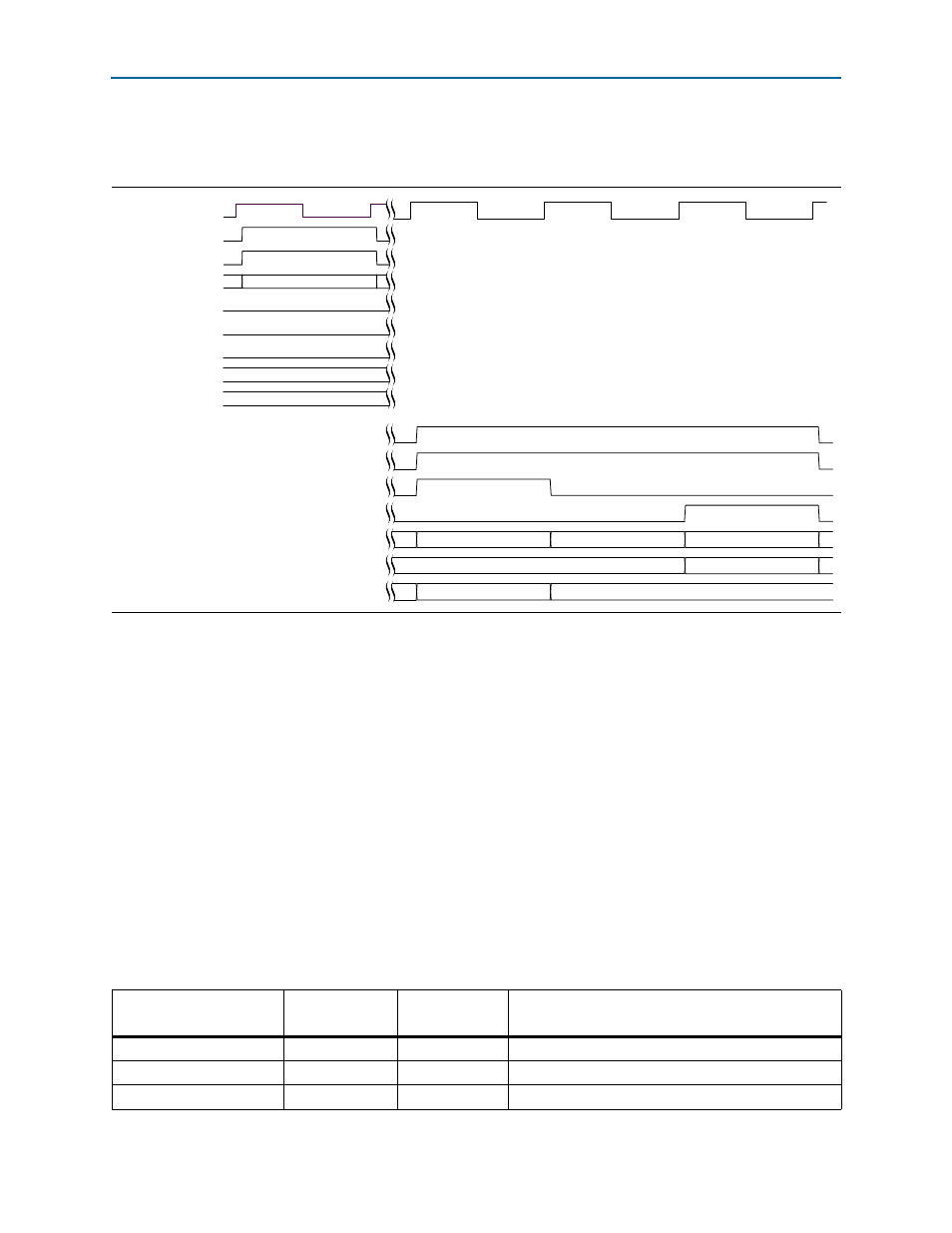

shows the behavior of the signals on the Avalon-ST pass-through

interface for this example transaction sequence.

The following two sections describe the behavior shown in

■

■

NREAD Request Transaction

The NREAD request requires a single clock cycle. During this cycle, user logic asserts

gen_rx_hd_ready

to indicate it is ready to sample data. In the same cycle, the IP core

asserts gen_rx_hd_valid. Because both gen_rx_hd_ready and gen_rx_hd_valid are

asserted, the current cycle is an Avalon-ST ready cycle on the header Avalon-ST

interface. The IP core provides valid header information on gen_rx_hd_data for the

user logic to sample.

The IP core does not assert gen_rx_pd_valid, because the NREAD request transaction

contains no payload data.

lists the header fields of the request packet in this example.

Figure 4–24. Avalon-ST Pass-Through Interface NREAD Request Receive and Response Send Example

clk

gen_tx_ready

gen_tx_valid

gen_tx_empty[3:0]

gen_tx_packet_size[8:0]

gen_tx_startofpacket

gen_tx_endofpacket

gen_tx_data[127:0]

gen_rx_hd_ready

gen_rx_hd_valid

0052DDDDAAAA4CBB765432100000

009DAAAADDDD80BB0011223344556677

028

8899AABBCCDDEEFF0123456789ABCDEF

FEDCBA98765432100000000000000000

8

gen_rx_hd_data[114:0]

gen_rx_pd_valid

gen_rx_pd_startofpacket

gen_rx_pd_endofpacket

gen_rx_pd_data[127:0]

gen_rx_pd_empty[2:0]

Table 4–40. NREAD Request Receive Example: RapidIO Header Fields in gen_rx_hd_data Bus (Part 1 of 2)

Field

gen_rx_hd_data

Bits

Value

Comment

pd_size[8:0]

[114:106]

9’h000

An NREAD request transaction has no payload data.

VC

[105]

0

The RapidIO II IP core supports only VC0.

CRF

[104]

0