Altera RapidIO II MegaCore Function User Manual

Page 92

4–50

Chapter 4: Functional Description

Logical Layer Interfaces

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

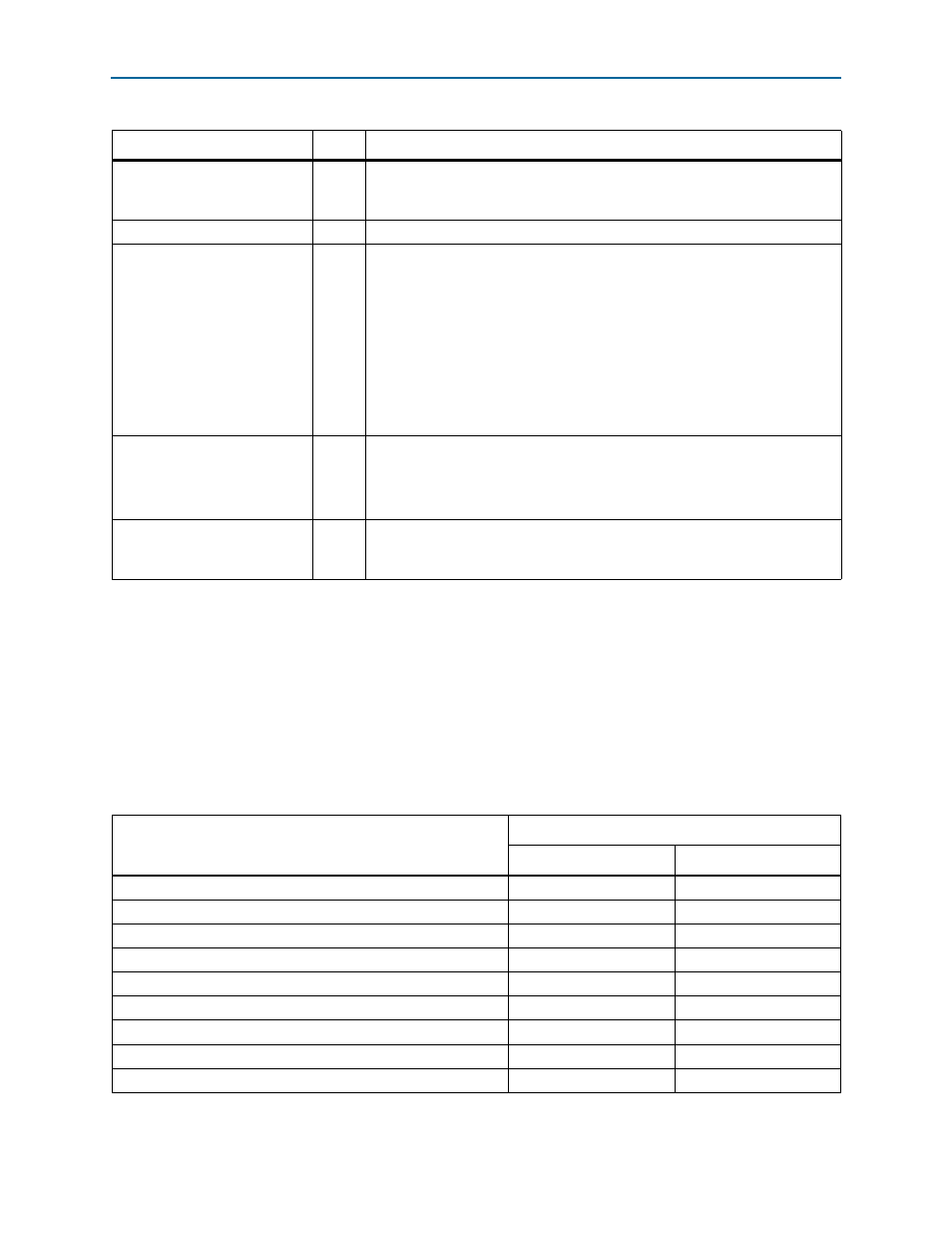

Table 4–25

list the required format of the TX header information on the

gen_tx_data

bus for both device ID widths. The required format derives directly from

the RapidIO specification. You must include the header information in the clock cycle

in which you assert gen_tx_startofpacket. Note that the ackID field is filled by the IP

core, and the eight-bit device ID fields are not extended with zeroes, in contrast to the

destinationID and source ID fields in gen_rx_hd_data.

gen_tx_startofpacket

Input

Marks the active cycle containing the start of the packet. The user logic asserts

gen_tx_startofpacket

and gen_tx_valid to indicate that a packet is

available for the IP core to sample.

(1)

gen_tx_endofpacket

Input

Marks the active cycle containing the end of the packet.

(1)

gen_tx_data[127:0]

Input

A 128-bit wide data bus. Carries the bulk of the information transferred from the

source to the sink.

(1)

The RapidIO II IP core fills in the RapidIO packet ackID field and adds the CRC

bits and padding bytes, but otherwise copies the bits from gen_tx_data to the

RapidIO packet without modifying them. Therefore, you must pack the

appropriate RapidIO packet fields in the correct RapidIO packet format in the

most significant bits of the gen_tx_data bus, gen_tx_data[127:N]. The

total width (127 – N + 1) of the header fields depends on the transaction and the

device ID width, as shown in

, and in

Interface Usage Examples” on page 4–56

gen_tx_empty[3:0]

Input

This bus identifies the number of empty bytes on the final data transfer of the

packet, which occurs during the clock cycle when gen_tx_endofpacket is

asserted.

(1)

The number of empty bytes must always be even.

gen_tx_packet_size[8:0]

Input

Indicates the number of valid bytes in the packet being transferred. The IP core

samples this signal only while gen_tx_startofpacket is asserted. User logic

must ensure this signal is correct while gen_tx_startofpacket is asserted.

:

(1) gen_tx_valid is used to qualify all the other input signals of the transmit side of the Avalon-ST pass-through interface.

(2) This signal is not defined in th

. However, it refers to data being transferred on the Avalon-ST sink interface.

Table 4–24. Avalon-ST Pass-Through Interface Transmit Side (Avalon-ST Sink) Signals (Part 2 of 2)

Signal Name

Type

Function

Table 4–25. RapidIO Header Information Format on gen_tx_data Bus

Field

gen_tx_data Bits

Device ID Width 8

Device ID Width 16

ackID[5:0]

[127:122]

[127:122]

VC

[121]

[121]

CRF

[120]

[120]

prio[1:0]

[119:118]

[119:118]

tt[1:0]

[117:116]

[117:116]

ftype[3:0]

[115:112]

[115:112]

destinationID[<deviceIDwidth>–1:0]

[111:104]

[111:96]

sourceID[<deviceIDwidth>–1:0]

[103:96]

[95:80]

specific_header

[95:...]

[79:...]