Status packet and error monitoring signals, Low latency signals, Status packet and error monitoring signals” on – Altera RapidIO II MegaCore Function User Manual

Page 127

Chapter 5: Signals

5–3

Physical Layer Signals

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

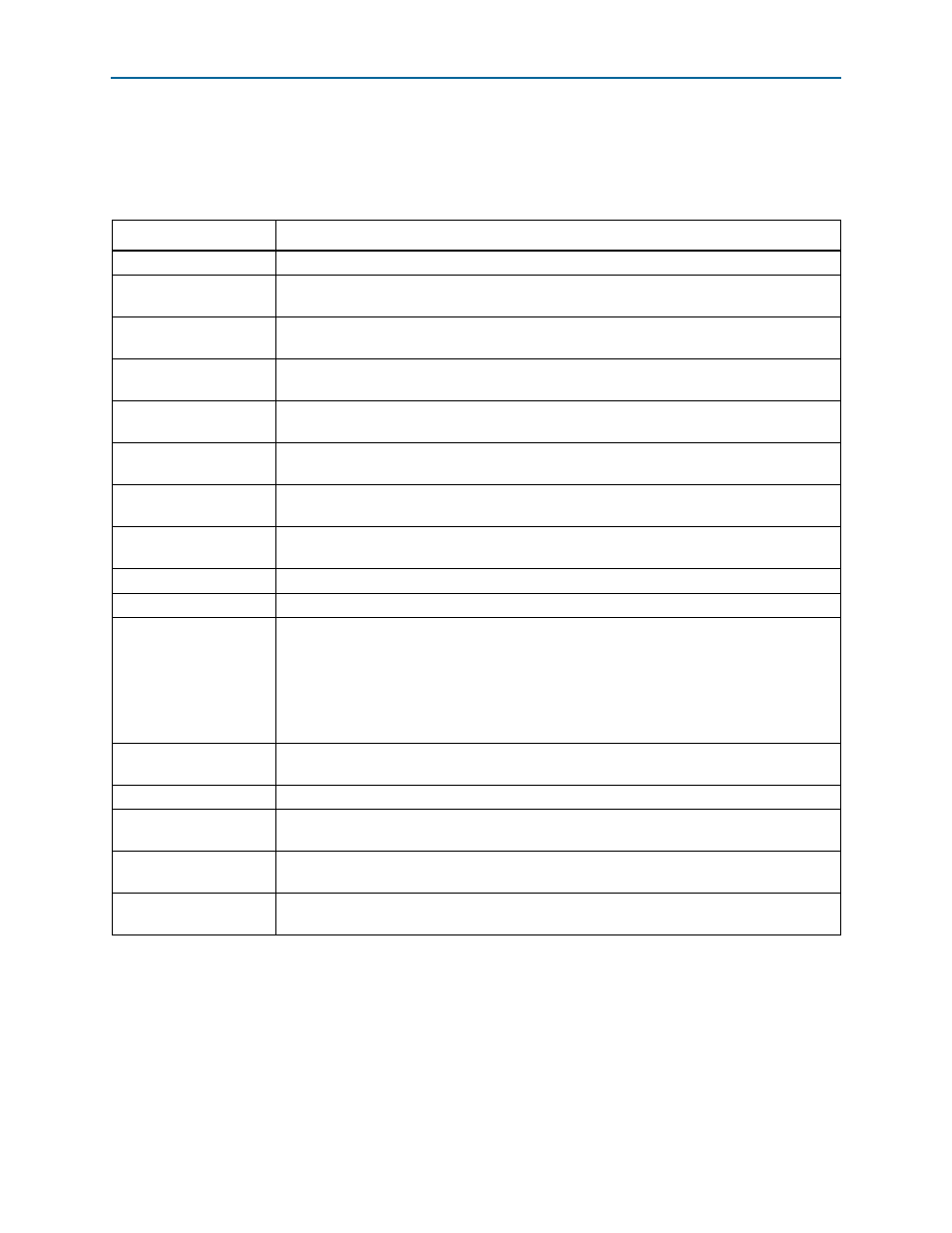

Status Packet and Error Monitoring Signals

Table 5–4

lists the status packet and error monitoring signals. All of these signals are

output signals synchronized with the sys_clk clock.

Low Latency Signals

The low-latency signals connect to the lowest level of the Physical layer module, to

minimize latency.

Table 5–5

list the low-latency signals.

Table 5–4. Status Packet and Error Monitoring

Output Signal

Description

packet_transmitted

Pulsed high for one clock cycle when a packet’s transmission completes normally.

packet_cancelled

Pulsed high for one clock cycle when a packet’s transmission is cancelled by sending a stomp,

a restart-from-retry, or a link-request control symbol.

packet_accepted_cs_

sent

Pulsed high for one clock cycle when a packet-accepted control symbol has been

transmitted.

packet_accepted_cs_

received

Pulsed high for one clock cycle when a packet-accepted control symbol has been received.

packet_retry_cs_

sent

Pulsed high for one clock cycle when a packet-retry control symbol has been transmitted.

packet_retry_cs_

received

Pulsed high for one clock cycle when a packet-retry control symbol has been received.

packet_not_accepted

_cs_sent

Pulsed high for one clock cycle when a packet-not-accepted control symbol has been

transmitted.

packet_not_accepted

_cs_received

Pulsed high for one clock cycle when a packet-not-accepted control symbol has been

received.

packet_crc_error

Pulsed high for one clock cycle when a CRC error is detected in a received packet.

control_symbol_error

Pulsed high for one clock cycle when a corrupted control symbol is received.

port_initialized

Indicates that the RapidIO initialization sequence has completed successfully.

This is a level signal asserted high while the initialization state machine is in the 1X_MODE,

2X_MODE, or 4X_MODE state, as described in paragraph 4.12 of the RapidIO Interconnect

Specification v2.2 Part 6: LP-Serial Physical Layer Specification.

This signal holds the inverse of the value of the PORT_UNINIT field of the Port 0 Error and

Status

CSR (offset 0x158) described in

.

port_error

This signal holds the value of the PORT_ERR bit of the Port 0 Error and Status CSR (offset

0x158

) described in

.

link_initialized

Indicates that the RapidIO port successfully completed link initialization.

port_ok

This signal holds the value of the PORT_OK bit of the Port 0 Error and Status CSR (offset

0x158

) described in

.

four_lanes_aligned

Indicates that all four lanes of the 4× RapidIO port are in sync and aligned. This signal is present

only in variations that support four lanes.

two_lanes_aligned

Indicates that the both lanes of the 2× RapidIO port are in sync and aligned. This signal is

present only in variations that support two lanes.