Table 6–92, Table 6–91, Table 6–90 – Altera RapidIO II MegaCore Function User Manual

Page 193: Table 6–93

Chapter 6: Software Interface

6–55

Transport and Logical Layer Registers

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

INFORMATION

[7:0]

RO

LSB of the information field of an outbound DOORBELL

message that has been confirmed as successful or

unsuccessful.

8'h0

Note to

:

(1) The completed Tx DOORBELL message comes directly from the Tx Doorbell Completion FIFO.

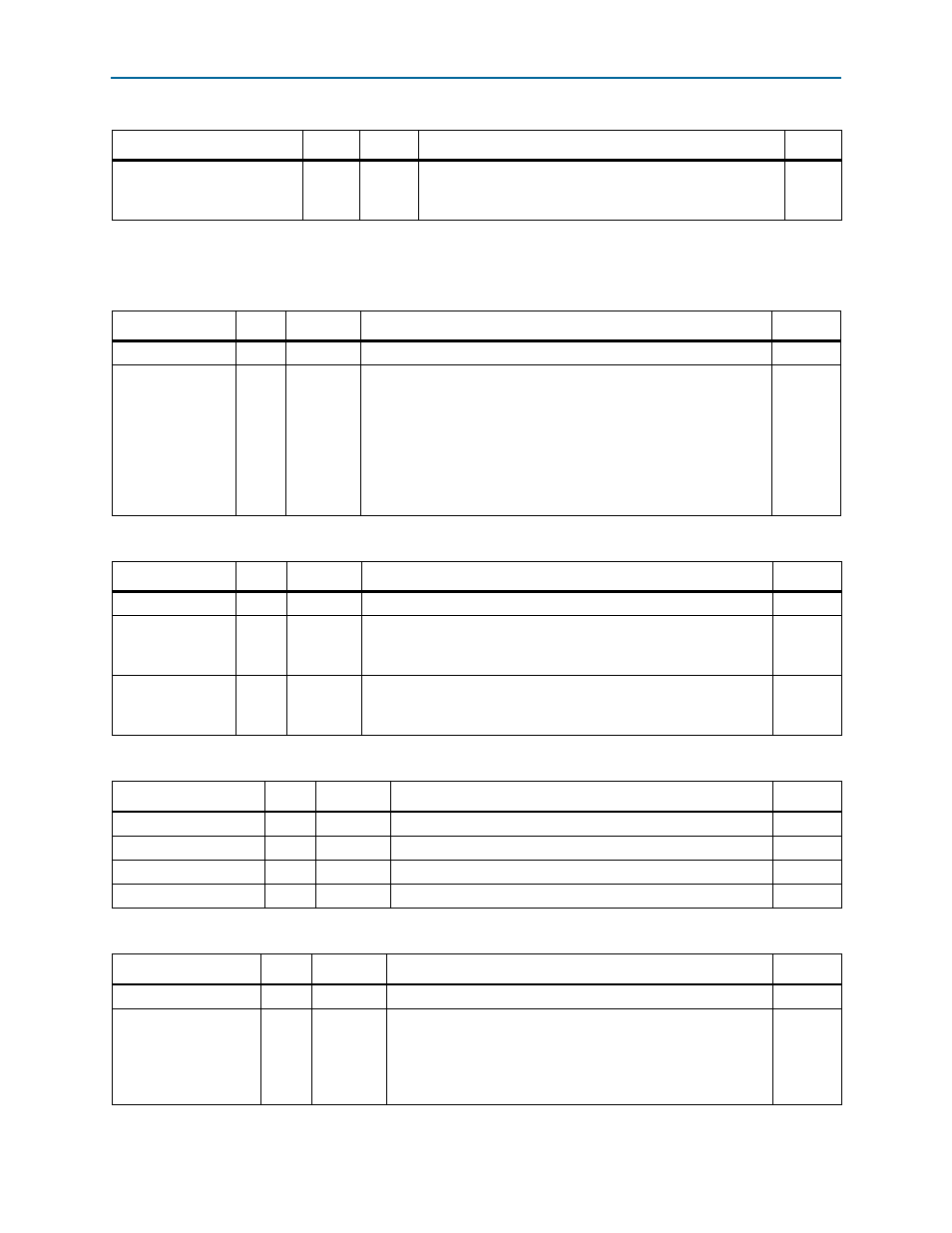

Table 6–89. Tx Doorbell Completion—Offset: 0x14

(1)

(Part 2 of 2)

Field

Bits

Access

Function

Default

Table 6–90. Tx Doorbell Completion Status—Offset: 0x18

Field

Bits

Access

Function

Default

RSRV

[31:2]

RO

Reserved

30'h0

ERROR_CODE

[1:0]

RO

This error code corresponds to the most recently read message from

the Tx Doorbell Completion register. After software reads the Tx

Doorbell

Completion register, a read to this register should follow

to determine the status of the message.

2'b00—Response DONE status

2'b01—Response with ERROR status

2'b10—Time-out error

2'h0

Table 6–91. Tx Doorbell Status Control—Offset: 0x1C

Field

Bits

Access

Function

Default

RSRV

[31:2]

RO

Reserved

30'h0

ERROR

[1]

RW

If set, outbound DOORBELL messages that received a response with

ERROR

status, or were timed out, are stored in the Tx Completion

FIFO. Otherwise, no error reporting occurs.

1'h0

COMPLETED

[0]

RW

If set, responses to successful outbound DOORBELL messages are

stored in the Tx Completion FIFO. Otherwise, these responses are

discarded.

1'h0

Table 6–92. Doorbell Interrupt Enable—Offset: 0x20

Field

Bits

Access

Function

Default

RSRV

[31:3]

RO

Reserved

29'b0

TX_CPL_OVERFLOW

[2]

RW

Tx Doorbell Completion Buffer Overflow Interrupt Enable

1'h0

TX_CPL

[1]

RW

Tx Doorbell Completion Interrupt Enable

1'h0

RX

[0]

RW

Doorbell Received Interrupt Enable

1'h0

Table 6–93. Doorbell Interrupt Status—Offset: 0x24 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:3]

RO

Reserved

29'h0

TX_CPL_OVERFLOW

[2]

RW1C

Interrupt asserted due to Tx Completion buffer overflow. This bit

remains set until at least one entry is read from the Tx

Completion FIFO. After reading at least one entry, software

should clear this bit. It is not necessary to read all of the Tx

Completion FIFO entries.

1'h0