Altera RapidIO II MegaCore Function User Manual

Page 194

Advertising

6–56

Chapter 6: Software Interface

Transport and Logical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

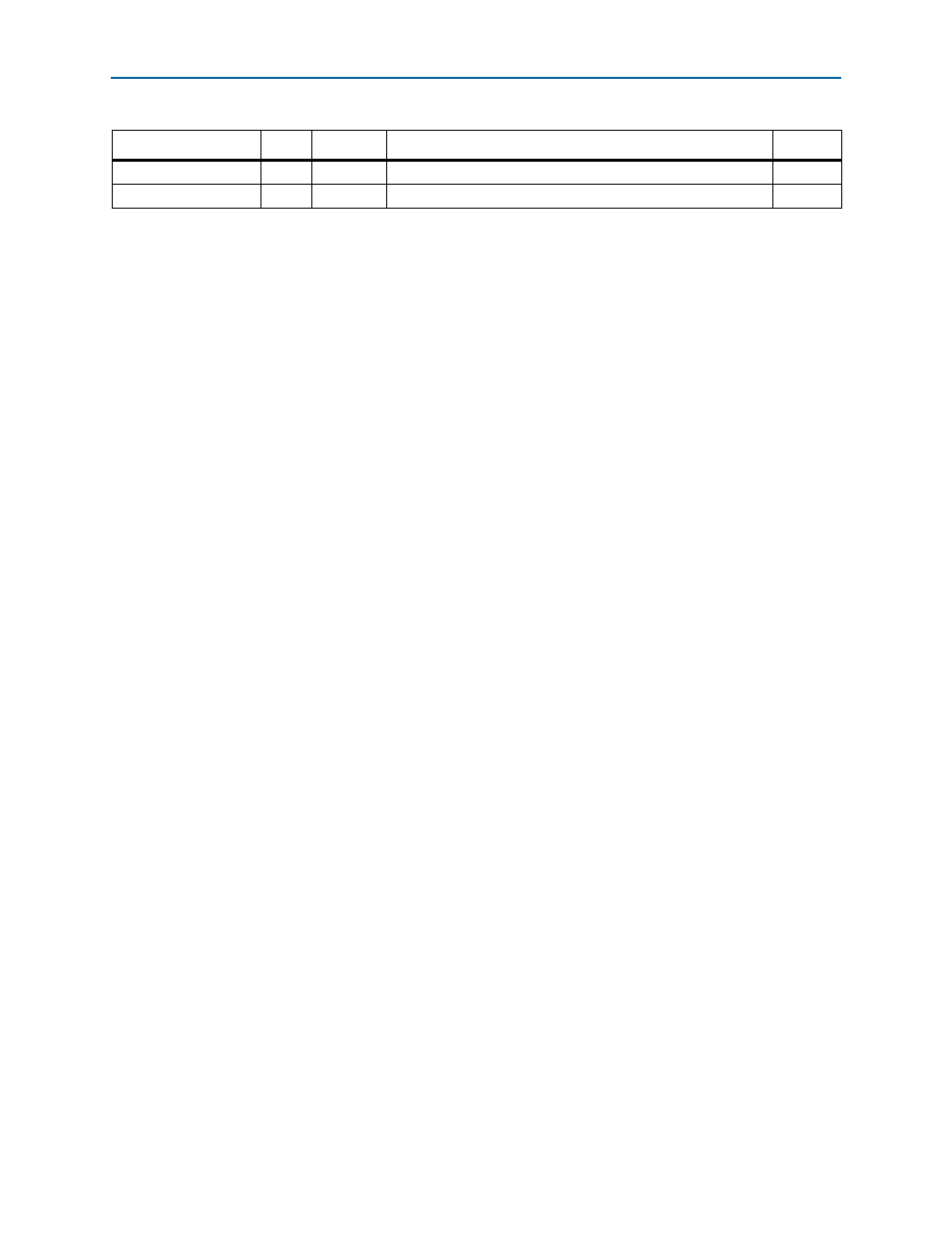

TX_CPL

[1]

RW1C

Interrupt asserted due to Tx completion status

1'h0

RX

[0]

RW1C

Interrupt asserted due to received messages

1'h0

Table 6–93. Doorbell Interrupt Status—Offset: 0x24 (Part 2 of 2)

Field

Bits

Access

Function

Default

Advertising