Performance and resource utilization, Performance and resource utilization –7 – Altera RapidIO II MegaCore Function User Manual

Page 15

Chapter 1: About The RapidIO II MegaCore Function

1–7

Performance and Resource Utilization

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

Performance and Resource Utilization

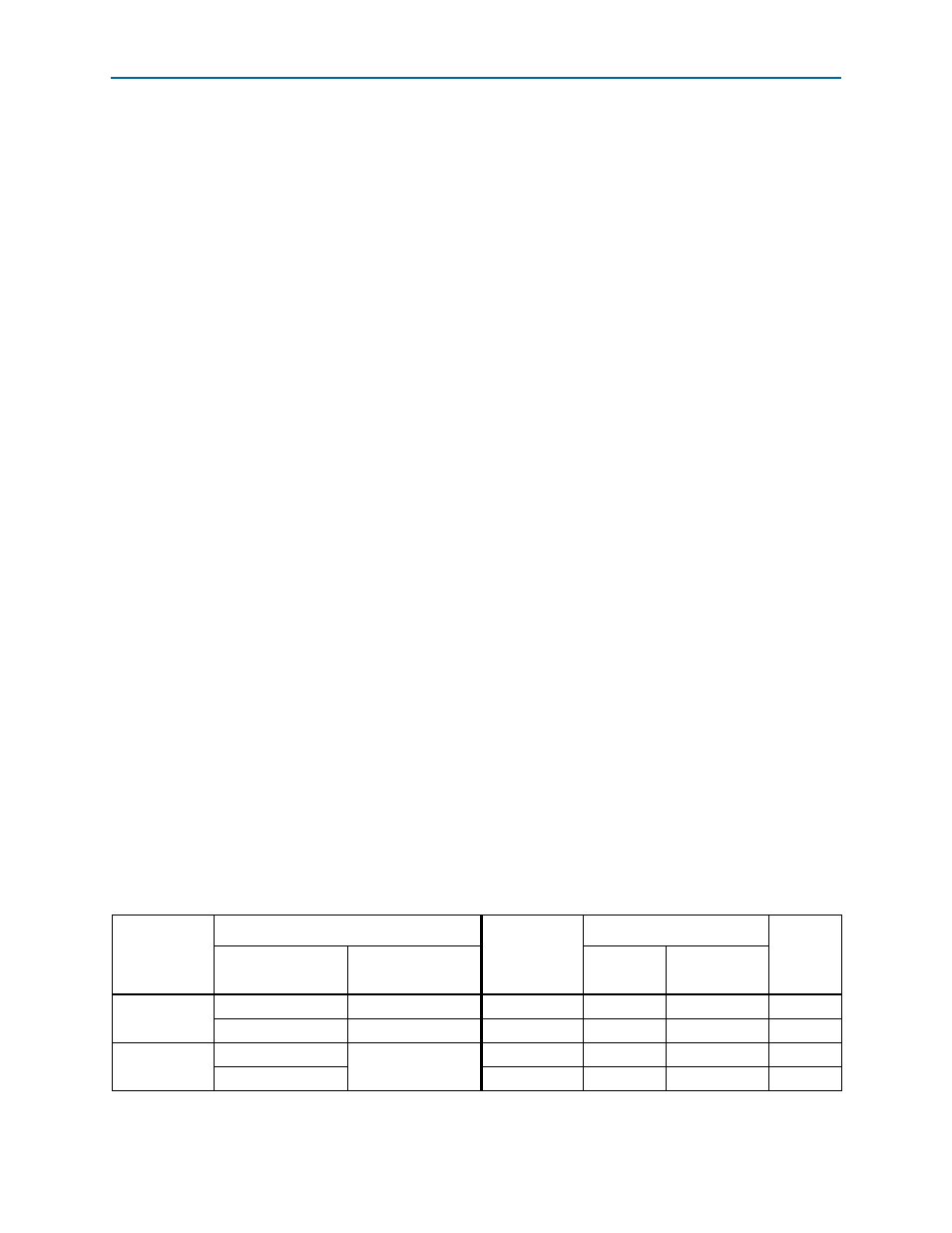

This section contains tables showing IP core variation sizes in the different device

families.

Table 1–3

lists the resources and expected performance for selected

variations that use these modules:

■

Minimal variation:

■

Physical layer

■

Transport layer

■

Avalon-ST pass-through interface

■

Full-featured variation:

■

Physical layer

■

Transport layer

■

Maintenance module

■

Doorbell module

■

Input/Output Avalon-MM master

■

Input/Output Avalon-MM slave

■

Error Management Registers block

All variations are configured with the following parameter settings:

■

Transceiver reference clock frequency of 156.25 MHz

■

The maximum RapidIO baud rate supported by the device

■

Support 1×, 2×, and 4× modes of operation

The numbers of ALMs, primary logic registers, and secondary logic registers in

Table 1–3

are rounded up to the nearest 100.

Table 1–3

shows results obtained using the Quartus II software v12.1 SP1 or Quartus

II software v14.0 Arria 10 Edition for the following devices:

■

Arria 10 (10AX048E2F29E2LG) (v14.0 Arria 10 Edition)

■

Arria V (5AGXFB3H4F35I5) (v12.1 SP1)

■

Cyclone V (5CGXFC7C6U19I7) (v12.1 SP1)

■

Stratix V (5SGXEA7H3F35C3) (v12.1 SP1)

Table 1–3. RapidIO II IP Core FPGA Resource Utilization (Part 1 of 2)

Device

Parameters

ALMs

Registers

Memory

Blocks

(M10K or

M20K

(1)

)

Variation

Baud Rate (Gbaud)

Primary

Secondary

Arria 10

Minimal

6.25

14300

14300

1100

31

Full-featured

6.25

20300

25300

1900

49

Arria V

Minimal

6.25

14800

13800

1700

41

Full-featured

24400

27500

2700

68