Altera RapidIO II MegaCore Function User Manual

Page 210

B–2

Appendix B: Differences Between RapidIO II MegaCore Function v12.1 and RapidIO MegaCore Function v12.1

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

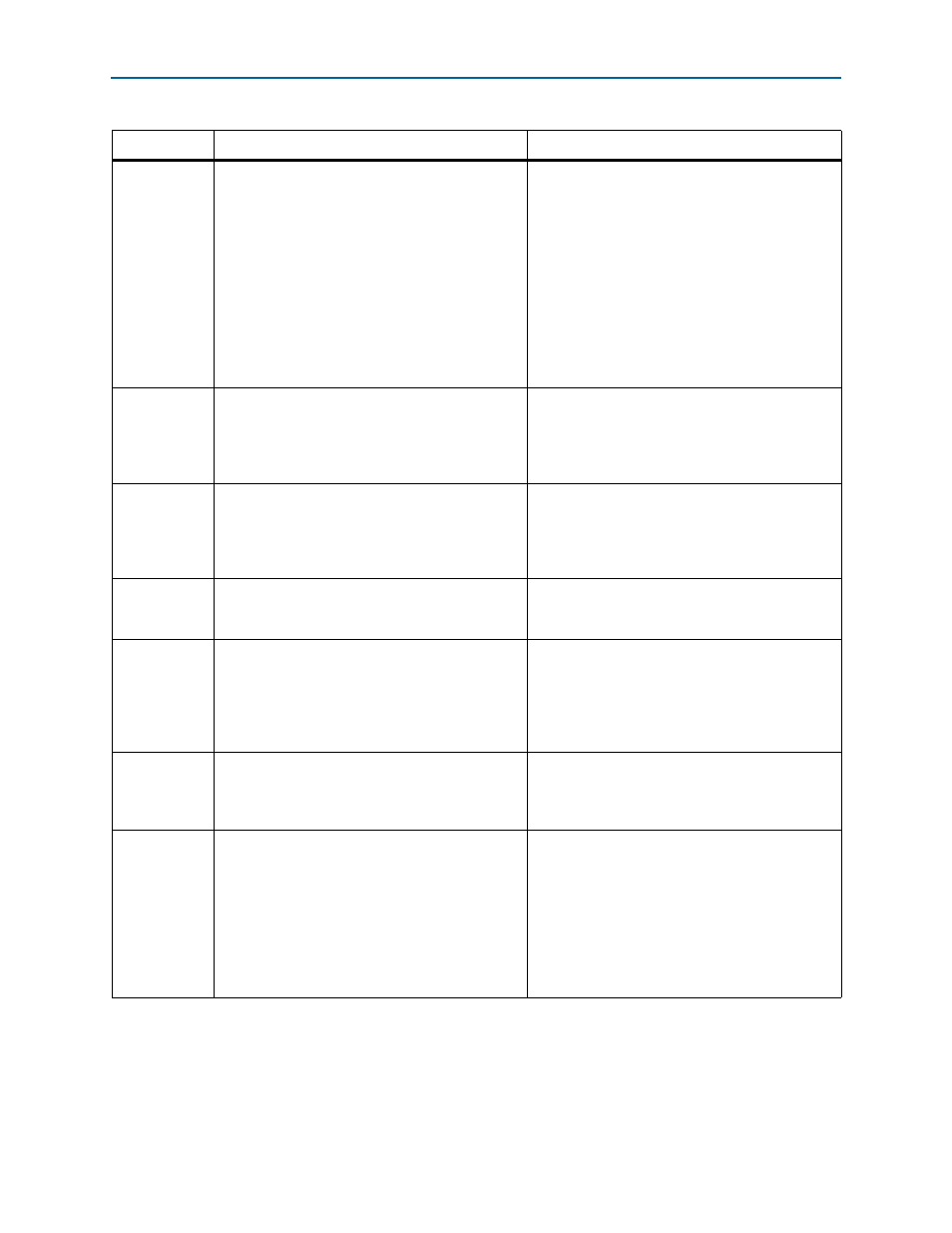

Avalon-MM

interface width

I/O Logical layer Master and Slave modules each

have a 128-bit wide Rx interface and a 128-bit wide

Tx interface. Doorbell and Maintenance modules

each have one 32-bit wide Avalon-MM interface in

each direction.

I/O Logical layer Master and Slave modules in a 1×

variation each have a 32-bit wide Rx interface and a

32-bit Tx interface, and I/O Logical layer Master and

Slave modules in a 4× variation each have a 64-bit

wide Rx interface and a 64-bit Tx interface. Doorbell

and Maintenance modules each have one 32-bit

wide Avalon-MM interface in each direction, in 1×

and 4× variations.

Update: With the introduction of 2x variations in the

RapidIO IP core v13.0, the I/O Logical layer Master

and Slave modules in a 2x variation each have a 64-

bit wide Rx interface and a 64-bit Tx interface.

I/O Logical

layer Master

Avalon-MM

read and write

ports

I/O Logical layer Master module has a single

Avalon-MM interface for read and write

transactions.

I/O Logical layer Master module has one

Avalon-MM interface for read transactions and a

separate Avalon-MM interface for write

transactions.

I/O Logical

layer Slave

Avalon-MM

read and write

ports

I/O Logical layer Slave module has a single

Avalon-MM interface for read and write

transactions.

I/O Logical layer Slave module has one Avalon-MM

interface for read transactions and a separate

Avalon-MM interface for write transactions.

CRC

Physical layer removes all CRC bits and padding

bytes from packets received from the RapidIO link.

Physical layer removes the 16-bit CRC that follows

the 80th received byte of a RapidIO packet, but not

the final CRC nor the padding bytes.

Behavior in

SILENT state

Transmitter is turned off while the initialization state

machine is in the SILENT state.

In 5.0 Gbaud variations, the transmitter is turned off

while the initialization state machine is in the

SILENT state. However, in 1.25, 2.5, and

3.125 Gbaud variations, the transmitters send a

continuous stream of K28.5 characters, all of the

same disparity, in the SILENT state.

Remote host

access to IP

core registers

Handles incoming read and write MAINTENANCE

requests with address in the appropriate range to

the local register set, internally.

Requires that your system connect the Maintenance

master interface to the Register Access slave

interface. The RapidIO IP core does not implement

this routing internally.

Maintenance

module

supported

operations

If you include a Maintenance module in your

RapidIO II IP core, it has both master and slave

ports, and supports MAINTENANCE read and write

operations and MAINTENANCE port-write

operations.

If you include a Maintenance module in your

RapidIO IP core, you can choose whether to

support an Avalon-MM master port or an Avalon-

MM slave port, or both. if your Maintenance module

supports the Avalon-MM slave port, you can

independently select whether to support

MAINTENANCE TX port-write

operations or

MAINTENANCE RX port-write

operations, or

both.

Table B–1. Major Differences Between the RapidIO II IP Core v12.1 and the RapidIO IP Core v12.1 (Part 2 of 4)

Property

RapidIO II IP Core v12.1

RapidIO IP Core v12.1