Altera RapidIO II MegaCore Function User Manual

Page 160

6–22

Chapter 6: Software Interface

Physical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

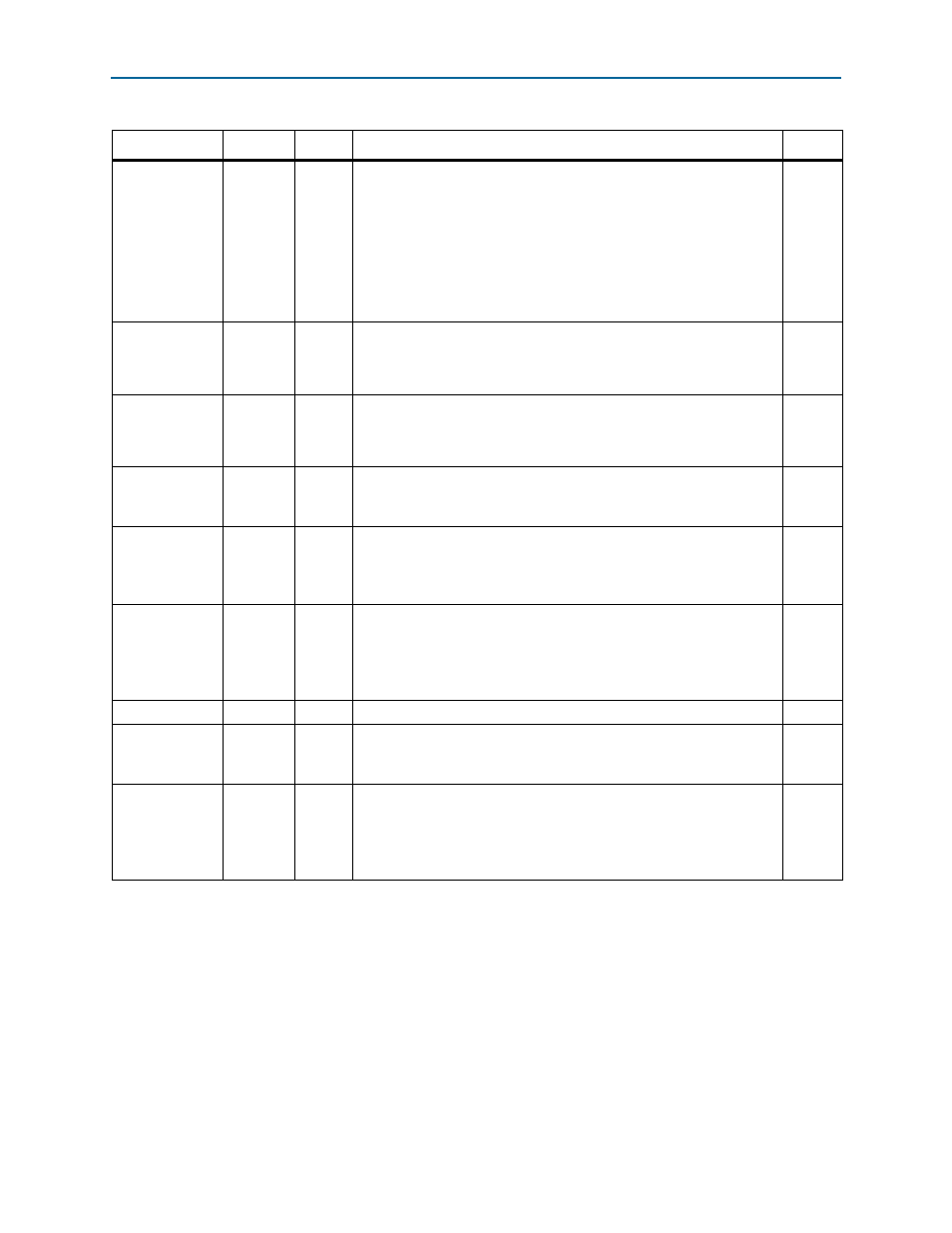

Receiver

Trained

[14]

RO

If the lane receiver controls any transmit or receive adaptive

equalization, this bit indicates whether all of the adaptive equalizers that

this lane controls are now trained. The value of this field is the value in

the Receiver trained bit in the CS field the lane transmits.

1’b0: The lane receiver controls one or more adaptive equalizers and

at least one of these adaptive equalizers is not trained.

1’b1: The lane receiver controls no adaptive equalizers, or all of the

adaptive equalizers it controls are trained.

1’b0

Receiver Lane

Sync

[13]

RO

Indicates the state of the lane n lane_sync signal.

1’b0: lane_sync is FALSE.

1’b1: lane_sync is TRUE.

1’b0

Receiver Lane

Ready

[12]

RO

Indicates the state of the lane n lane_ready signal.

1’b0: lane_ready is FALSE.

1’b1: lane_ready is TRUE.

1’b0

8B10B_DEC_ERR

[11:8]

RC

Number of 8B10B decoding errors detected on this lane since this

register bit was last read. The value saturates at 0xF (it does not roll

over). Reading the register resets this field to the value of 0.

4’h0

Lane_sync

State Change

[7]

RC

Indicates the state of the lane_sync signal for this lane has changed

since this bit was last read. Reading the register resets this bit to the

value of 1’b0. This bit provides an indication of the burstiness of the

transmission errors that the lane receiver detected.

1’b0

Rcvr_trained

State Change

[6]

RO

Indicates the state of the rcvr_trained signal for this lane has

changed since this bit was last read. Reading the register resets this bit

to the value of 1’b0. A change in the signal value indicates that the

training state of the adaptive equalization under the control of this

receiver has changed; frequent changes indicate a problem on the lane.

1’b0

RSRV

[5:4]

RO

Reserved

2’b0

Status 1 CSR

Implemented

[3]

RO

Indicates whether the RapidIO implementation includes the Lane n

Status 1 CSR

for the current lane n. The RapidIO II IP core

implements this register, so this bit always has the value of 1’b1.

1’b1

Status 2–7

CSRs

Implemented

[2:0]

RO

Number of implementation-specific Lane n Status m CSRs for the

current lane n. The RapidIO II IP core implements the Lane n Status 2,

Lane n Status 3, and Lane n Status 4 CSRs, so this field always has the

value of 2’b011. For the value encoding, refer to RapidIO Interconnect

Specification v2.2 Part 6: LP-Serial Physical Layer Specification.

3’b011

Note to

:

(1) Reflects the choice made in the RapidIO II parameter editor.

Table 6–17. LP-Serial Lane n Status 0—Offset: 0x210, 0x230, 0x250, 0x270 (Part 2 of 2)

Field Bits

Access

Function

Default