Altera RapidIO II MegaCore Function User Manual

Page 20

2–2

Chapter 2: Getting Started

IFiles Generated for Altera IP Cores (Legacy Parameter Editor)

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

I

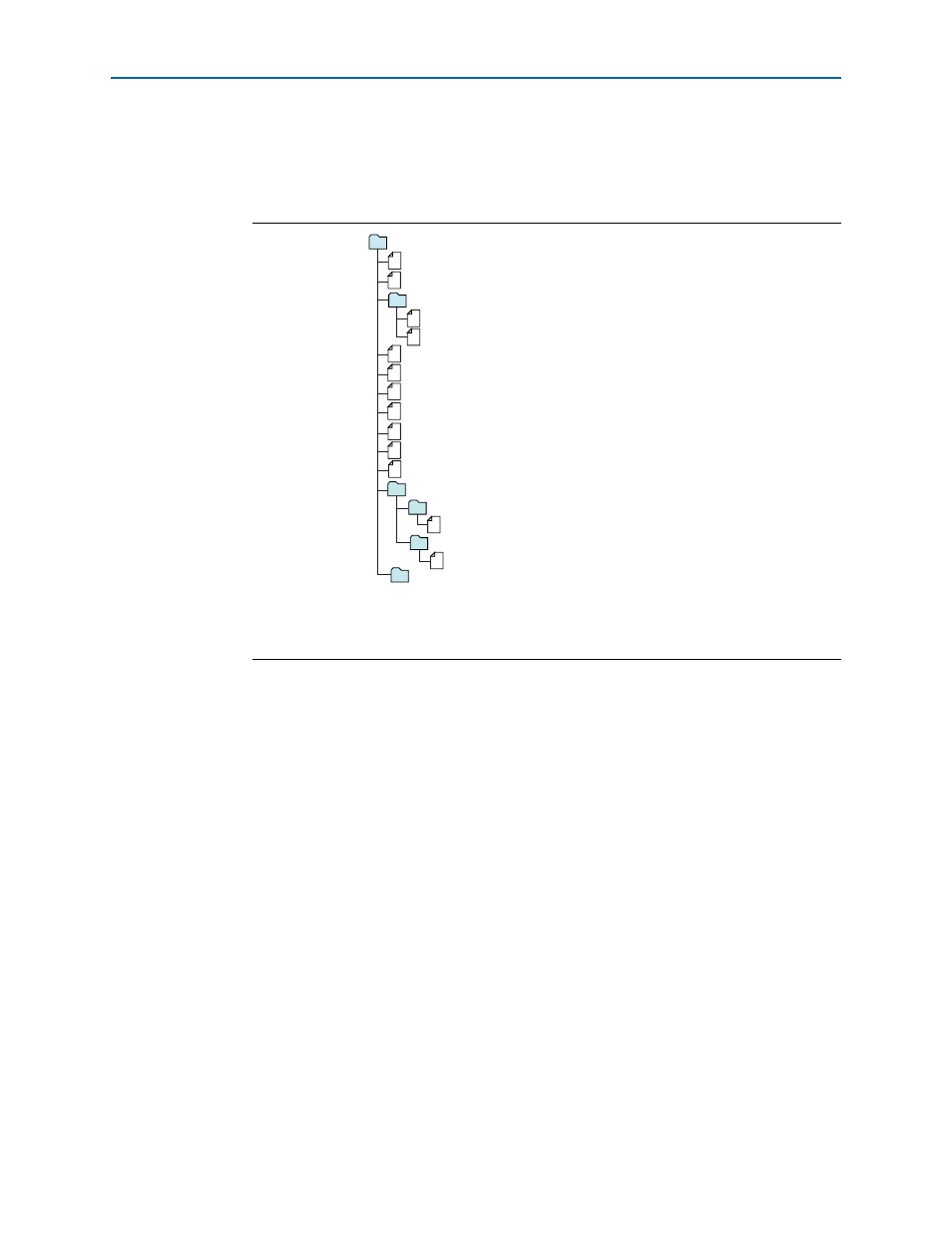

Files Generated for Altera IP Cores (Legacy Parameter Editor)

The Quartus II software version 14.0 and previous parameter editor generates the

following output file structure for Altera IP cores:

In the case of the RapidIO II IP core you generate from the Quartus II IP Catalog in the

Quartus II software v14.0 Arria 10 Edition:

■

The testbench script appears in <your_ip>_sim/<vendor>.

■

The testbench files appear in <your_ip>_sim/altera_rapidio2/tb.

■

The IP core simulation files appear in <your_ip>_sim/altera_rapidio2/<vendor>.

The RapidIO II IP core does not generate an example design.

Figure 2–1. IP Core Generated Files (Legacy Parameter Editor)

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

<Project Directory>

<your_ip>_sim

1

<Altera IP>_instance.vo - IPFS model

2

<simulator_vendor>

<simulator setup scripts>

<your_ip>.qip - Quartus II IP integration file

<your_ip>.sip - Lists files for simulation

<your_ip>_testbench or _example

- testbench or example design

1

<your_ip>.v, .sv. or .vhd - Top-level IP synthesis file

<Altera IP_name>_instance

<your_ip>_syn.v or .vhd - Timing & resource estimation netlist

1

<your_ip>.cmp - VHDL component declaration file

<your_ip>.bsf - Block symbol schematic file

<your_ip> - IP core synthesis files

<your_ip>.sv, .v, or .vhd - HDL synthesis files

<your_ip>.sdc - Timing constraints file

<your_ip>.ppf - XML I/O pin information file

1

<your_ip>.spd - Combines individual simulation scripts

1

<your_ip>_sim.f - Refers to simulation models and scripts

1