Altera RapidIO II MegaCore Function User Manual

Page 66

4–24

Chapter 4: Functional Description

Logical Layer Interfaces

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

■

Increments the COMPLETED_OR_CANCELLED_WRITES field of the Input/Output Slave

RapidIO Write Requests

register (

) if the transaction is a

write request.

User logic can clear an interrupt by writing 1 to the interrupt register’s corresponding

bit location.

The Avalon-MM slave interface burstcount and byteenable signals determine the

values of the RapidIO packet header fields wdptr and rdsize or wrsize.

Burstcount and Byteenable Encoding in RapidIO Packets” on page 4–27

describes the

conversion.

The RapidIO II IP core copies the values you program in the PRIORITY and

DESTINATION_ID

fields of the control register for the matching window, to the RapidIO

packet header fields prio and destinationID, respectively.

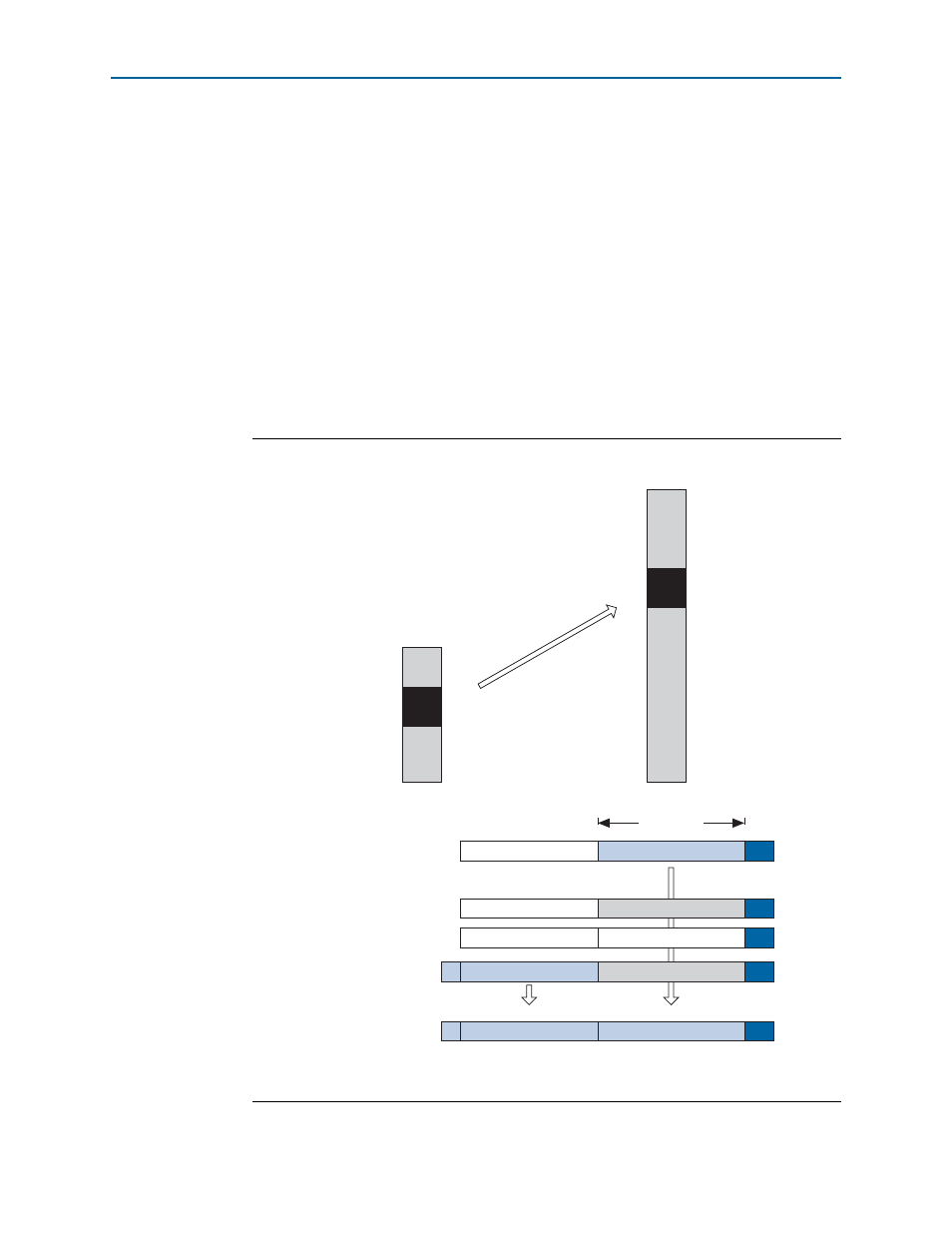

shows the I/O slave Logical window translation process.

Figure 4–9. Input/Output Slave Window Translation

Note to

:

(1) These bits must have the same value in the initial Avalon-MM address and in the window base.

Base

Window

Offset

0x000000000

0x3FFFFFFFF

RapidIO

Address Space

0x00000000

0xFFFFFFFF

Avalon-MM

Address Space

Initial

Avalon-MM Address Bits

Don’t Care

Don’t Care

33

Window Base

Window Mask

Window Offset

Resulting

RapidIO Address

0

3

4

0

3

4

31

31

XAMO

(1)

(1)

Window Size

11111111.........................11 000000000000000..............00