Preserving transaction order, Preserving transaction order –45, Figure 4–20 – Altera RapidIO II MegaCore Function User Manual

Page 87

Chapter 4: Functional Description

4–45

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

■

Error Management module that reports detected errors, including the following

errors:

■

Unexpected response (a response packet was received, but its TransactionID

does not match any pending request that is waiting for a response).

■

Request time-out (an outbound DOORBELL request did not receive a response

from the target device).

Preserving Transaction Order

If you select Prevent doorbell messages from passing write transactions in the

RapidIO parameter editor, each DOORBELL message from the Avalon-MM interface is

kept in the Tx staging FIFO until all I/O write transactions that started on the write

Avalon-MM slave interface before this DOORBELL message arrived on the Doorbell

module Avalon-MM interface have been transmitted to the Transport layer. An I/O

write transaction is considered to have started before a DOORBELL transaction if the

ios_rd_wr_write

signal is asserted while the ios_rd_wr_waitrequest signal is not

asserted, on a cycle preceding the cycle on which the drbell_s_write signal is

asserted for writing to the Tx Doorbell register while the drbell_s_waitrequest

signal is not asserted.

If you do not select Prevent doorbell messages from passing write transactions in

the RapidIO II parameter editor, the Doorbell Tx staging FIFO is not configured in the

RapidIO II IP core.

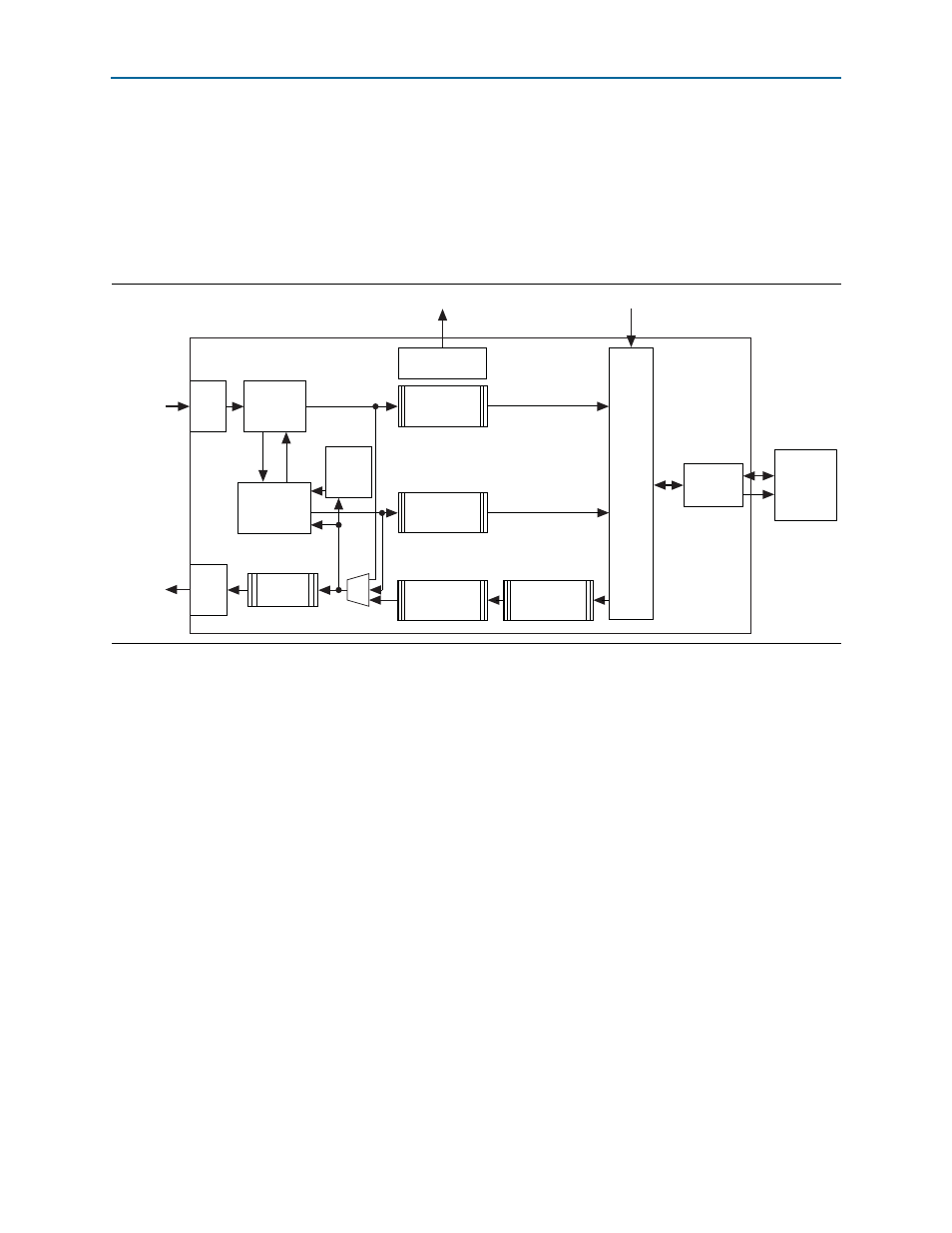

Figure 4–20. Doorbell Module Block Diagram

Sink

Rx Control

Source

Acknowledge

RAM

Doorbell Logical Module

From

Transport

Layer

Module

To

Transport

Layer

Module

To Register Module

From I/O Slave Module

Error

Management

Tx Output

FIFO

Rx

FIFO

IRQ

Avalon-MM

Slave

System

Interconnect

Fabric

Tx

FIFO

Tx Staging

FIFO

Tx Completion

FIFO

Tx

Timeout

Register

and

FIFO

Interface