Altera RapidIO II MegaCore Function User Manual

Page 82

4–40

Chapter 4: Functional Description

Logical Layer Interfaces

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

User Receiving MAINTENANCE Write Requests

Table 4–18

lists the Maintenance Avalon-MM interface usage example this section

describes.

The RapidIO II IP core generates write transfers on the Maintenance Avalon-MM

master interface in response to Type 8 MAINTENANCE Write request packets on the

RapidIO link with the following properties:

■

ttype

has the value of 4'b0001, indicating a MAINTENANCE Write request

■

config_offset

has a value that indicates an address outside the range of the

RapidIO II IP core internal register set

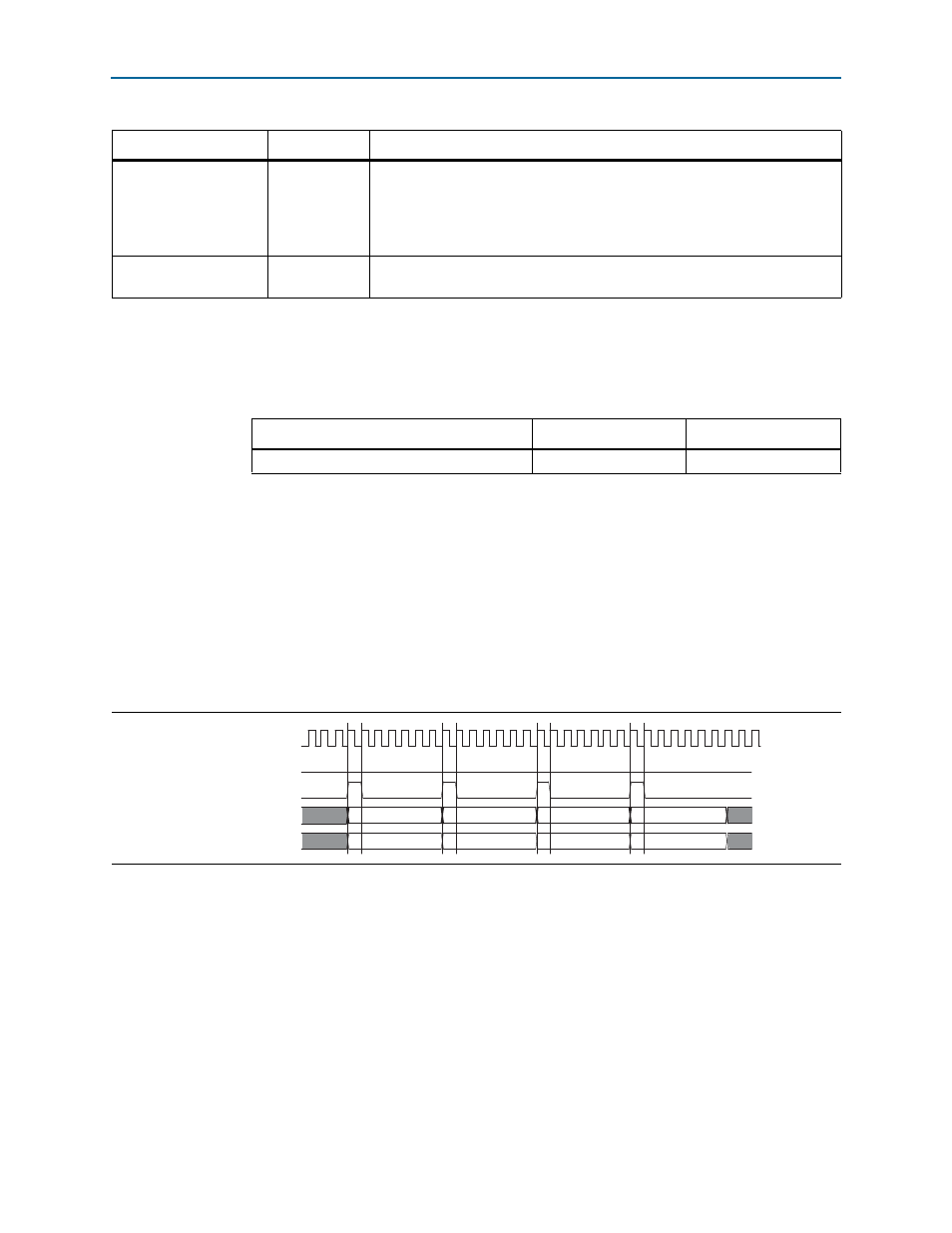

Figure 4–17

shows the signal relationships when the RapidIO II IP core presents a

sequence of four write transfers on the Maintenance Avalon-MM master interface.

In the first active clock cycle, the RapidIO II IP core indicates the start of a write

transfer by asserting the usr_mnt_write signal. Simultaneously, the IP core presents

the target address on the usr_mnt_address address bus and the data on the

usr_mnt_writedata

data bus.

In this example, user logic does not assert the usr_mnt_waitrequest signal. However,

when user logic asserts the usr_mnt_waitrequest signal during a write transfer, the IP

core maintains the address and data values on the buses until at least one clock cycle

after user logic deasserts the usr_mnt_waitrequest signal. User logic can use the

usr_mnt_waitrequest

signal to throttle requests on this interface until it is ready to

process them.

hop_count

The IP core assigns to this field the value programmed in the HOP_COUNT field

of the Tx Maintenance Mapping Window n Control register (

) for the matching address translation window n. Refer to

“Defining the Maintenance Address Translation Windows” on page 4–34

for

matching details.

payload[63:0]

The IP core assigns the value of mnt_s_writedata[31:0] to the appropriate

half of this field.

Table 4–17. Maintenance Write Request Transmit Example: RapidIO Packet Fields (Part 2 of 2)

Field

Value

Comment

Table 4–18. Maintenance Interface Usage Example: Receiving MAINTENANCE Write Request

User Operation

Device ID Width

Payload Size (Bytes)

Receive MAINTENANCE write request

8

32

Figure 4–17. Write Transfers on the Maintenance Avalon-MM Master Interface

4

8

C

10

ACACACAC

5C5C5C5C

BEEFBEEF

FACEFACE

usr_mnt_write

usr_mnt_writedata

usr_mnt_address

usr_mnt_waitrequest

system clock