Testbench completion, Testbench completion –10 – Altera RapidIO II MegaCore Function User Manual

Page 204

7–10

Chapter 7: Testbench

Testbench Completion

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

The testbench performs this test five times. All testbench port-write operations have a

payload of 32 bytes. Each operation is performed one of the sis_sys_mnt_master_bfm

or sys_mnt_master_bfm read_write_cmd or read_data tasks.

Transactions Across the Avalon-ST Pass-Through Interface

The demonstration testbench tests the Avalon-ST pass-through interface by

generating some transactions with invalid destinationID values. The DUT should

route these packets to the Avalon-ST pass-through interface. The testbench generates

these transactions only if the DUT has Disable destination ID checking by default

turned off.

Testbench Completion

The testbench concludes by checking that all of the packets have been received. If no

error is detected and all packets are received, the testbench issues a TESTBENCH PASSED

message stating that the simulation was successful.

If an error is detected, a TESTBENCH FAILED message is issued to indicate that the

testbench has failed. A TESTBENCH INCOMPLETE message is issued if the expected

number of checks is not made. For example, this message is issued if not all packets

are received before the testbench is terminated. The variable tb_rio.exp_chk_cnt

determines the number of checks done to ensure completeness of the testbench.

To generate a value change dump file called dump.vcd for all viewable signals,

uncomment the line //$dumpvars(0,tb_rio) in the tb_rio.sv file.

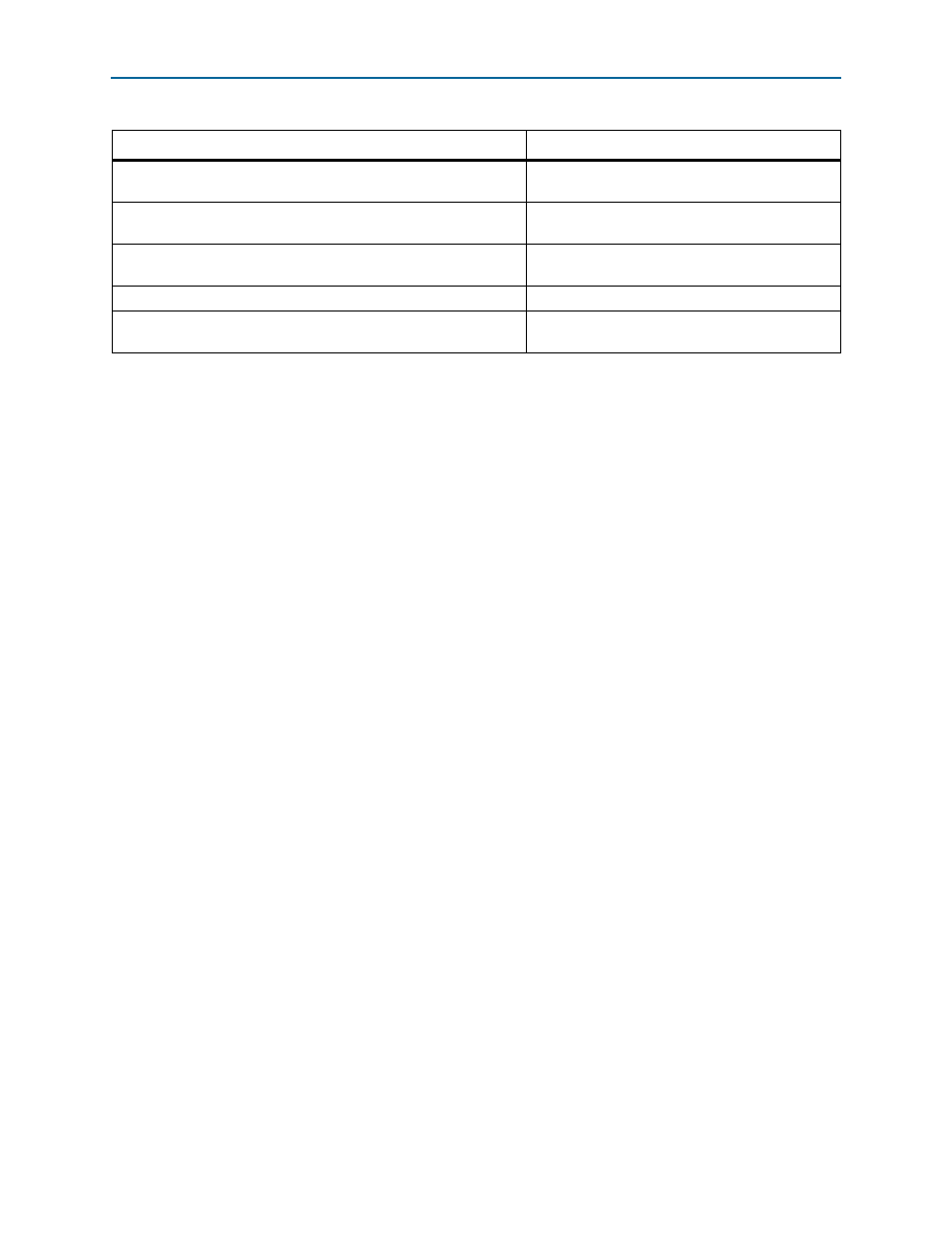

Verifies that the sister_rio module has the interrupt bit

PACKET_STORED

set

Read register at address 0x10080

Retrieves the Port-Write payload from the sister_rio module and

checks for data integrity

Read registers at addresses 0x10260–0x1029C

Checks the sister_rio module Rx Port Write Status register for

correct payload size

Read register at address 0x10254

Clears the PACKET_STORED interrupt in the sister_rio module

Write 1 to bit 4 of register at address 0x10080

Waits for the next interrupt at the sister _rio module

Monitor the sister_rio module mnt_mnt_s_irq

signal

Table 7–5. Port-Write Test

Operation

Action