Input/output logical layer modules, Input/output logical layer modules –9 – Altera RapidIO II MegaCore Function User Manual

Page 51

Chapter 4: Functional Description

4–9

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

The interface supports the following interrupt lines:

■

std_reg_mnt_irq

—when enabled, the interrupts registered in the CSRs and Error

Management registers assert the std_reg_mnt_irq signal.

■

io_m_mnt_irq

—this interrupt signal reports interrupt conditions related to the I/O

Avalon-MM master interface. When enabled, the interrupts registered in the

Input/Output Master Interrupt

register at offset 0x103DC assert the

io_m_mnt_irq

signal.

■

io_s_mnt_irq

—this interrupt signal reports interrupt conditions related to the I/O

Avalon-MM slave interface. When enabled, the interrupts registered in the

Input/Output Slave Interrupt

register at offset 0x10500 assert the io_s_mnt_irq

signal.

■

mnt_mnt_s_irq

—this interrupt signal reports interrupt conditions related to the

Maintenance interface slave port. When enabled, the interrupts registered in the

Maintenance

Interrupt register at offset 0x10080 assert the

mnt_mnt_s_irq

signal.

Input/Output Logical Layer Modules

This section describes the following Input/Output Logical layer modules:

■

“Input/Output Avalon-MM Master Module”

■

“Input/Output Avalon-MM Slave Module” on page 4–19

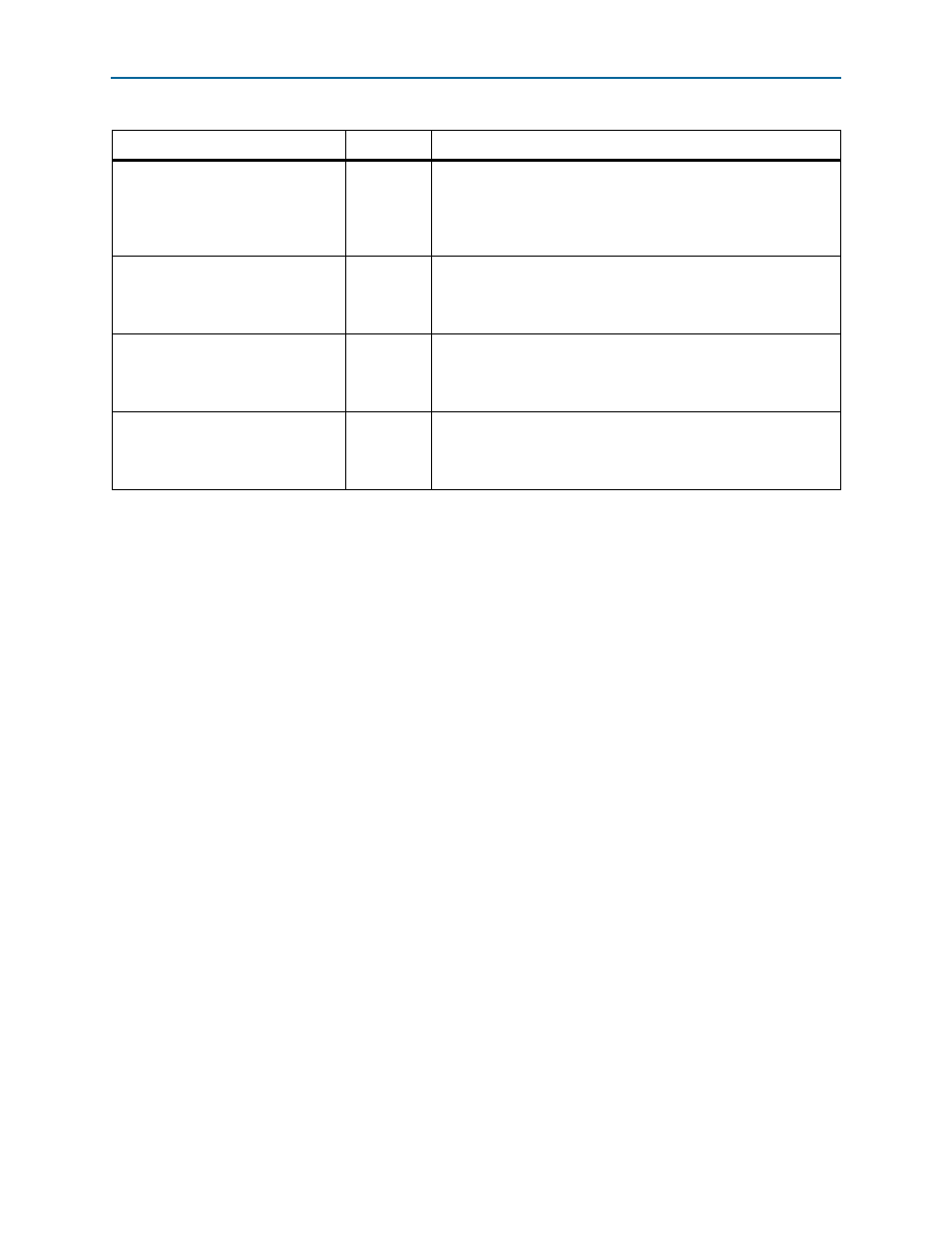

std_reg_mnt_irq

Output

Standard registers interrupt request. This interrupt signal is

associated with the error conditions registered in the Command and

Status Registers (CSRs) and the Error Management Extensions

registers. Refer to

“Command and Status Registers (CSRs)” on

and

“Error Management Registers” on page 6–42

.

io_m_mnt_irq

Output

I/O Logical Layer Avalon-MM Master module interrupt signal. This

interrupt is associated with the conditions registered in the

Input/Output Master Interrupt

register at offset 0x103DC.

Refer to

io_s_mnt_irq

Output

I/O Logical Layer Avalon-MM Slave module interrupt signal. This

interrupt signal is associated with the conditions registered in the

Input/Output Slave Interrupt

register at offset 0x10500.

Refer to

mnt_mnt_s_irq

Output

Maintenance slave interrupt signal. This interrupt signal is

associated with the conditions registered in the Maintenance

Interrupt

register at offset 0x10080. Refer to

Table 4–4. Register Access Avalon-MM Slave Interface Signals (Part 2 of 2)

Signal

Direction

Description