Altera RapidIO II MegaCore Function User Manual

Page 159

Chapter 6: Software Interface

6–21

Physical Layer Registers

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

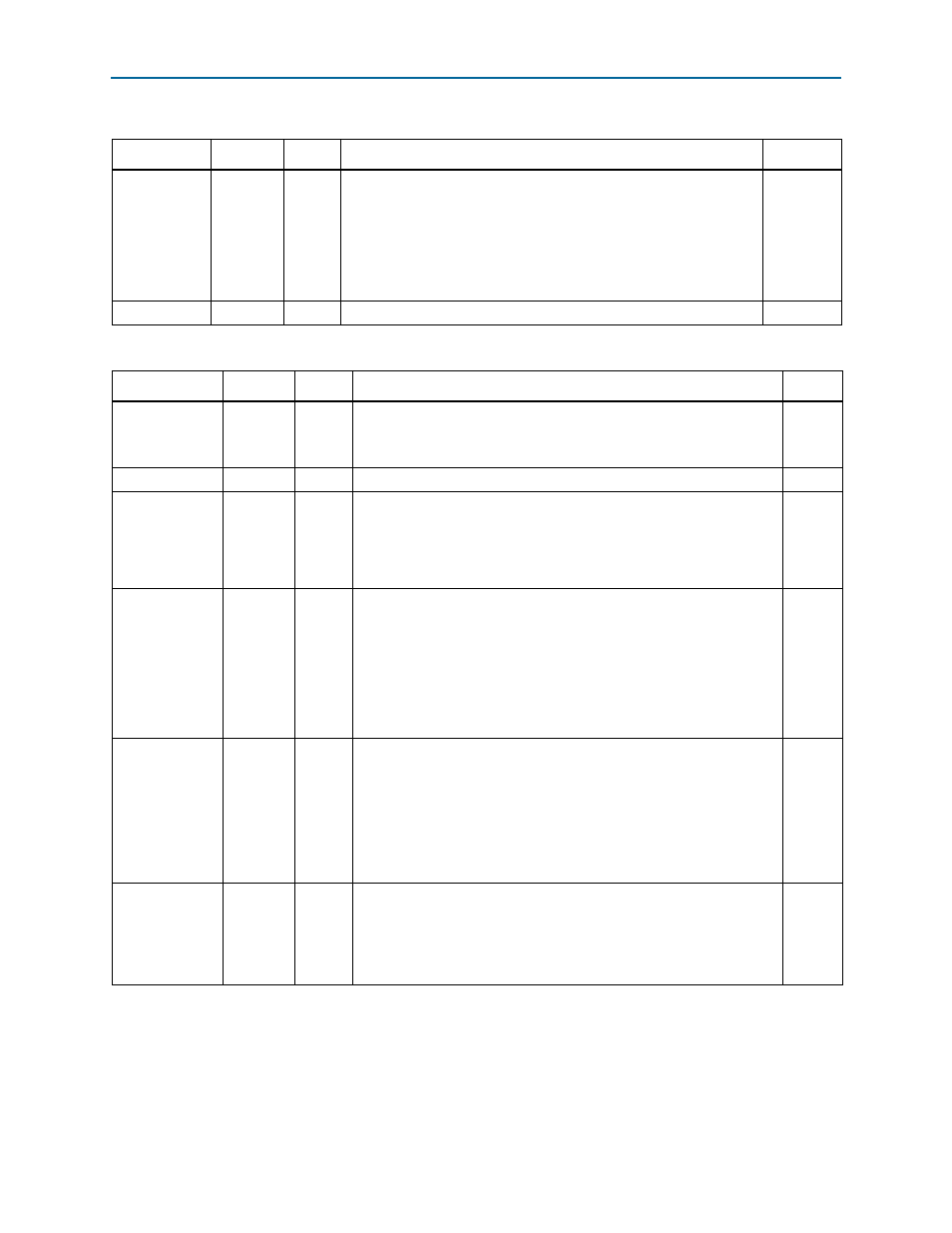

Table 6–16. LP-Serial Lane Register Block Header—0x200

Field Bits

Access

Function

Default

EF_PTR

[31:16] RO

Hard-wired pointer to the next block in the data structure, if one exists.

If this IP core variation instantiates the Error Management Extensions

registers, the value in this field is the address of the Error Management

Extended Features block, which is 0x300. If this IP core variation does

not instantiate the Error Management Extensions registers, the value of

this field is determined by the Extended features pointer parameter in

the RapidIO II parameter editor.

EF_ID

[15:0]

RO

Hard-wired extended features ID.

16'h000D

Table 6–17. LP-Serial Lane n Status 0—Offset: 0x210, 0x230, 0x250, 0x270 (Part 1 of 2)

Field Bits

Access

Function

Default

Port Number

[31:24] RO

The number of the port within the IP core to which the lane is assigned.

The RapidIO II IP core implements only a single RapidIO port, so this

field always has the value of 0.

8’h0

Lane Number

[23:20]

RO

The number of the lane in the port.

4’hn

Transmitter

Type

[19]

RO

Transmitter type.

1’b0: Short run.

1’b1: Long run.

This value is identical for all lanes of the port.

Transmitter

Mode

[18]

RW

Transmitter operating mode.

1’b0: Short run.

1’b1: Long run.

The value in this field is identical for all lanes and is identical to the value

of the Transmitter Type field. The value in this field does not affect

the physical transceiver. Software must modify this bit if relevant

physical transceiver properties change.

Receiver Type

[17:16]

RO

Receiver type.

2’b00: Short run.

2’b01: Medium run.

2’b10: Long run.

2’b11: Reserved.

This value is identical for all lanes of the port.

Receiver

Input

Inverted

[15]

RO

Indicates that the lane receiver has detected that the polarity of its input

signal is inverted, and has inverted the receiver input to correct the

polarity. A value of 1’b0 indicates the receiver input is not inverted.

The RapidIO II IP core does not support automatic detection of inverted

inputs, and this field always has the value of 0.

1’b0