Physical layer registers, Physical layer registers –6, Escribed in – Altera RapidIO II MegaCore Function User Manual

Page 144

6–6

Chapter 6: Software Interface

Physical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

Physical Layer Registers

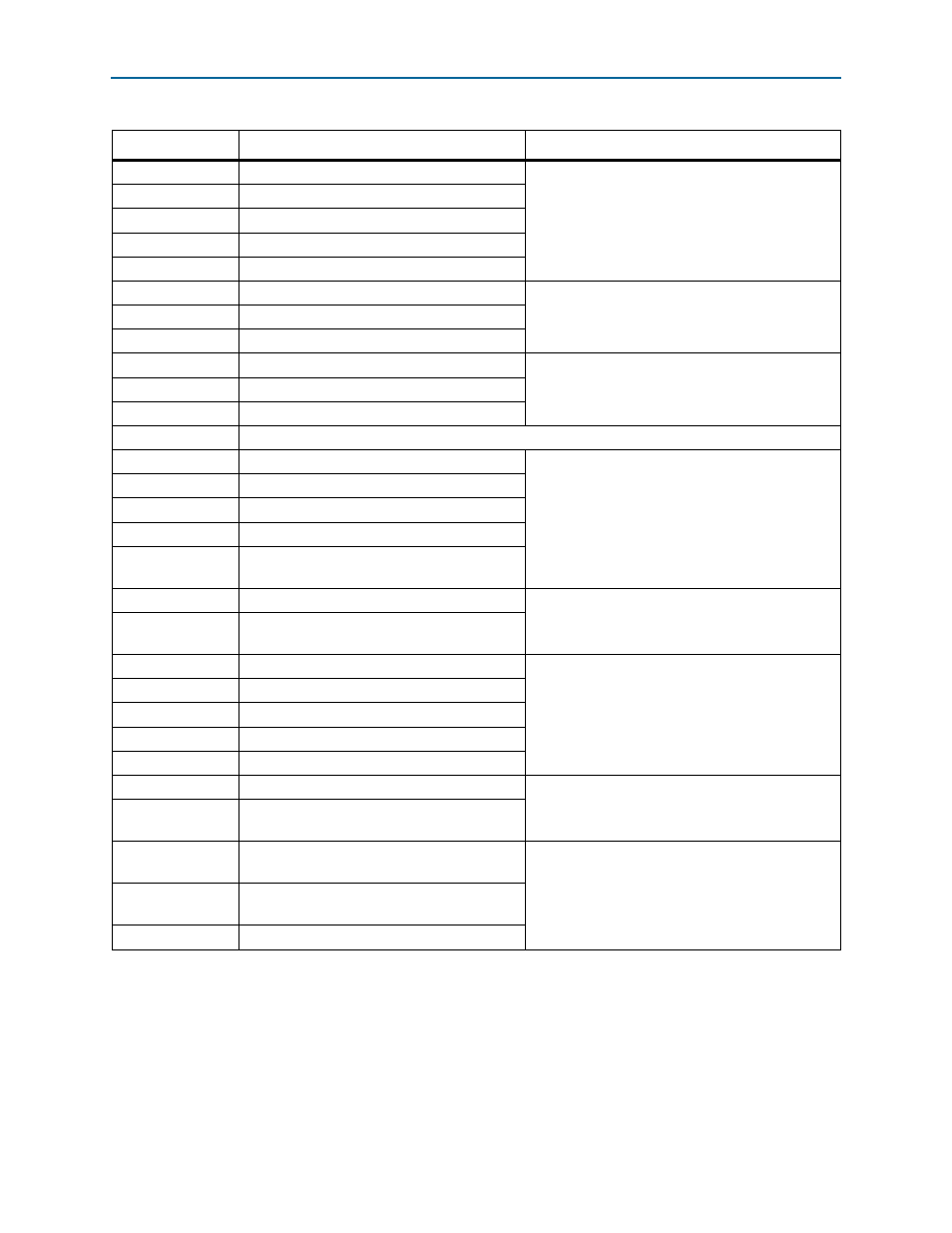

The RapidIO II IP core implements the following Physical layer registers in Extended

Features space:

■

All of the LP-Serial Extended Features block registers.

0x10100

Tx

Maintenance Window 0 Base

Maintenance module.

These registers are described in

Maintenance Registers” on page 6–35

0x10104

Tx

Maintenance Window 0 Mask

0x10108

Tx Maintenance

Window 0 Offset

0x1010C

Tx

Maintenance Window 0 Control

0x10110–0x1011C

Tx

Maintenance Windows 1

0x10200

Tx

Port Write Control

Maintenance module.

These registers are described in

0x10204

Tx

Port Write Status

0x10210–0x1024C

Tx

Port Write Buffer

0x10250

Rx

Port Write Control

Maintenance module.

These registers are described in

0x10254

Rx

Port Write Status

0x10260–0x1029C

Rx

Port Write Buffer

0x102A0–0x102FC

Reserved

0x10300

I/O

Master Window 0 Base

Input/Output Master Logical layer.

These registers are described in

Master Address Mapping Registers” on page 6–37

0x10304

I/O

Master Window 0 Mask

0x10308

I/O

Master Window 0 Offset

0x1030C

Reserved

0x10310–0x103F8

(with gaps)

I/O

Master Windows 1–15

0x103DC

I/O

Master Interrupt

Input/Output Master Logical layer.

These registers are described in

Master Interrupts” on page 6–38

.

0x103FC

I/O

Master Interrupt Enable

0x10400

I/O

Slave Window 0 Base

Input/Output Slave Logical layer.

These registers are described in

Mapping Registers” on page 6–39

0x10404

I/O

Slave Window 0 Mask

0x10408

I/O

Slave Window 0 Offset

0x1040C

I/O

Slave Window 0 Control

0x10410-0x104FC

I/O

Slave Windows 1–15

0x10500

I/O

Slave Interrupt

Input/Output Slave Logical layer.

These registers are described in

.

0x10504

I/O

Slave Interrupt Enable

0x10508

I/O Slave Pending NWRITE_R

Transactions

Input/Output Slave Logical layer.

These registers are described in

Pending Transactions” on page 6–41

0x1050C

I/O Slave Avalon-MM Write

Transactions

0x10510

I/O Slave RapidIO Write Requests

Table 6–4. Extended Features and Implementation-Defined Registers Memory Map (Part 3 of 3)

Address

Name

Used by Module