Altera RapidIO II MegaCore Function User Manual

Page 161

Chapter 6: Software Interface

6–23

Physical Layer Registers

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

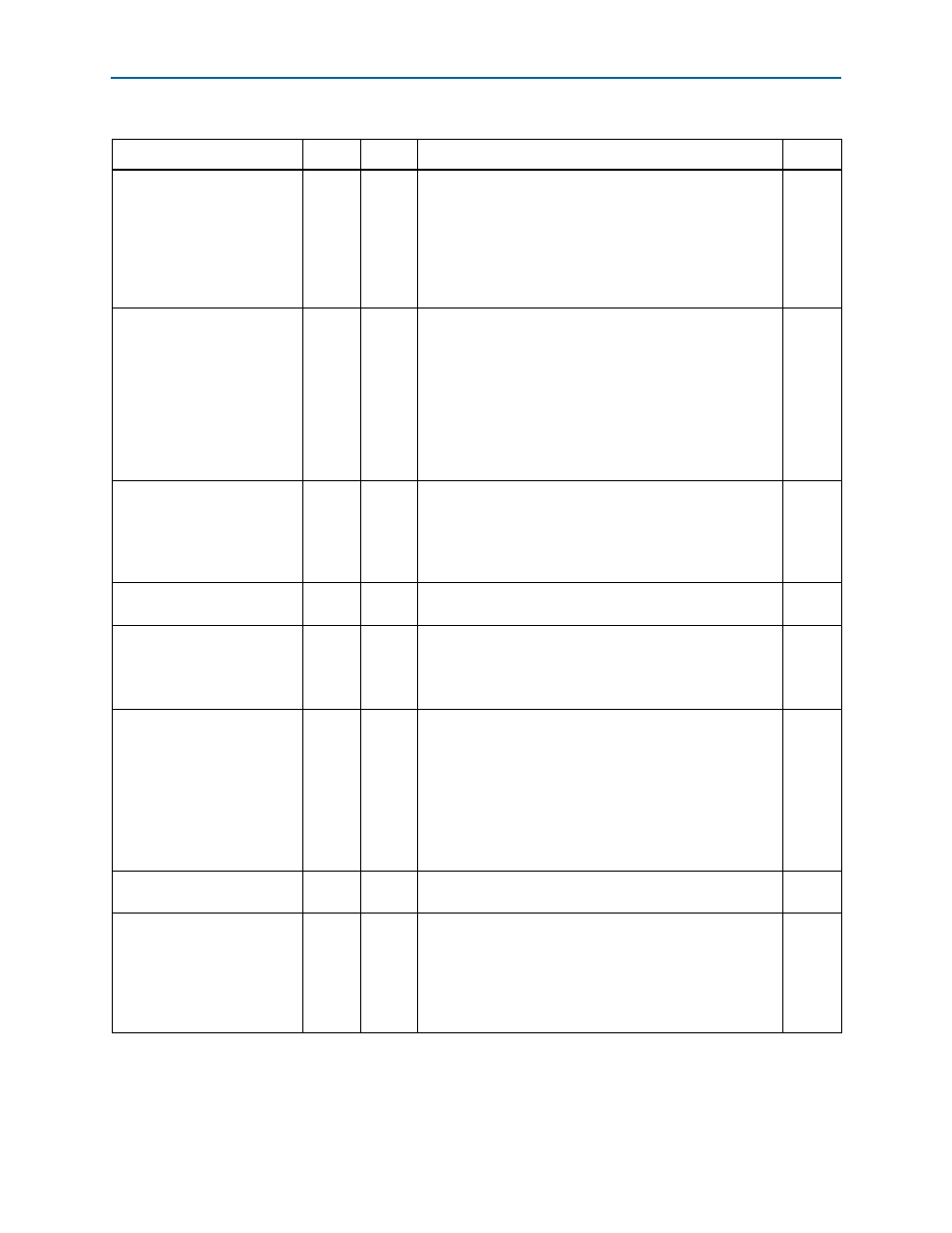

Table 6–18. LP-Serial Lane n Status 1—Far End Lane n Status—Offset: 0x214, 0x234, 0x254, 0x274 (Part 1 of 2)

Field Bits

Access

Function

Default

IDLE2 received

[31]

RW1C

Indicates whether an IDLE2 sequence has been received by

the lane since this field was last reset. To reset this bit, write

the value of 1’b1.

1’b0: No IDLE2 sequence has been received since the bit

was last reset.

1’b1: An IDLE2 sequence has been received since the bit

was last reset.

1’b0

IDLE2 information

current

[30]

RO

Indicates that the information in this register (collected from

the received IDLE2 sequence) is information from the most

recent IDLE2 control symbol marker and CS field that were

received by this lane without detected errors, and that the

lane’s lane_sync signal has remained asserted since the

most recent control symbol marker and CS field were

received.

1’b0: The IDLE2 information is not current.

1’b1: The IDLE2 information is current.

1’b0

Values changed

[29]

RO

Indicates whether the values of any of the other 31 bits in

this register have changed since the register was last read.

This bit is reset when the register is read.

1’b0: The values have not changed.

1’b1: One or more values have changed.

1’b0

Implementation defined

[28]

RO

Holds the value of the implementation-defined bit in the

received CS field.

1’b0

Connected port lane

receiver trained

[27]

RO

Indicates the receiver in the connected lane in the RapidIO

link partner is trained.

1’b0: Receiver not trained.

1’b1: Receiver trained.

1’b0

Received port width

[26:24]

RO

Received port width. This field supports the following valid

values:

3’b000: One lane.

3’b001: 2 lanes.

3’b010: 4 lanes.

3’b011: 8 lanes.

3’b100: 16 lanes.

The values 3’b101–3’b111 are reserved.

3’b000

Lane number in connected

port

[23:20]

RO

Number of the lane (0–15) in the connected port. Normally

the value should be n.

4’h0

Connected port transmit

emphasis Tap(–1) status

[19:18]

RO

Tap(–1) status of the RapidIO link partner on the connected

lane:

2’b00: Tap(–1) not implemented.

2’b01: Tap(–1) at minimum emphasis setting.

2’b10: Tap(–1) at maximum emphasis setting.

2’b11: Tap(–1) at intermediate emphasis setting.

2’b00