Altera RapidIO II MegaCore Function User Manual

Page 150

6–12

Chapter 6: Software Interface

Physical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

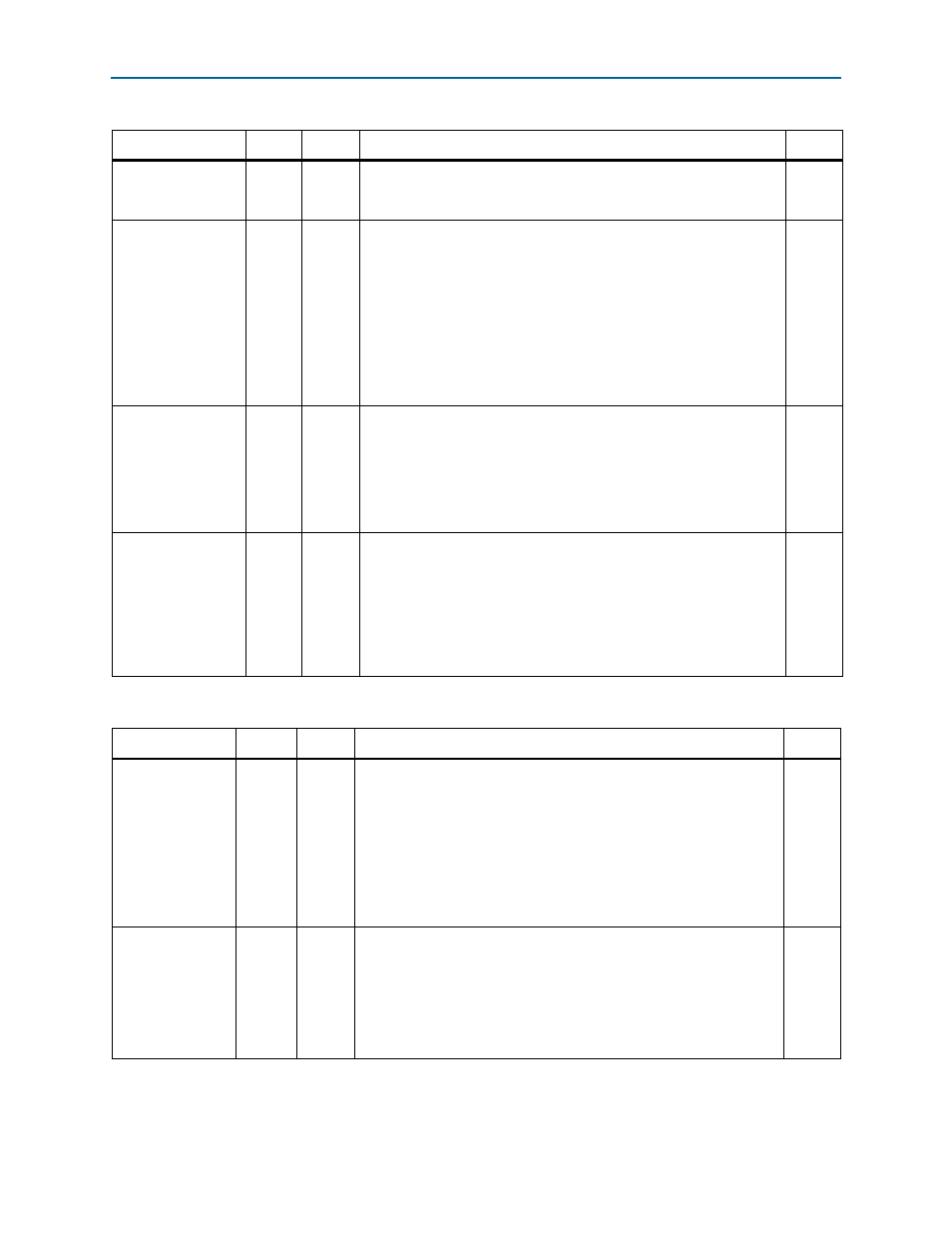

INACTIVE_LNS_EN

[3]

RO

Indicates whether the RapidIO implementation supports enabling

inactive lanes for testing. The RapidIO II IP core does not support

enabling inactive lanes for testing, so this bit always has the value of 0.

1'b0

DATA_SCRMBL_DIS

[2]

RW

Indicates whether data scrambling is disabled.

1’b0: The transmit scrambler and the receive descrambler are

enabled.

1’b1: The transmit scrambler and the receive descrambler are

disabled. However, the transmit scrambler remains enabled for the

generation of pseudo-random data characters for the IDLE2 random

data field.

This bit is for test use only. Do not assert this bit during normal

operation.

1'b0

REMOTE_TX_EMPH_S

UPPORT

[1]

RO

Indicates whether the port can transmit commands to control the

transmit emphasis in the connected port.

1’b0: The port does not support adjusting the transmit emphasis in

the connected port.

1’b1: The port supports adjusting the transmit emphasis in the

connected port.

1'b1

REMOTE_TX_EMPH_E

NABLE

[0]

RO

Indicates whether the port may transmit commands to control the

transmit emphasis in the connected port.

1’b0: Adjusting the transmit emphasis in the connected port is

disabled in this port.

1’b1: Adjusting the transmit emphasis in the connected port is

enabled in this port. This field can only have this value if

REMOTE_TX_EMPH_SUPPORT

has the value of 1.

1'b1

Table 6–13. Port 0 Control 2 CSR—Offset: 0x154

(1)

(Part 3 of 3)

Field

Bits

Access

Function

Default

Table 6–14. Port 0 Error and Status CSR—Offset: 0x158

(Part 1 of 5)

Field

Bits

Access

Function

Default

IDLE2_SUPPORT

[31]

RO

Indicates whether the port supports the IDLE2 sequence for baud rates

of 5.0 and below.

1’b0: Port does not support the IDLE2 sequence for baud rates of 5.0

and below.

1’b1: Port supports the IDLE2 sequence for baud rates of 5.0 and

below.

The RapidIO II IP core currently supports only the IDLE2 sequence, so

this bit always has the value of 1.

1'b1

IDLE2_ENABLE

[30]

RO

Indicates whether the the IDLE2 sequence is enabled in the RapidIO

implementation for baud rates of 5.0 and below.

1’b0:The IDLE2 sequence is disabled for baud rates of 5.0 and below.

1’b1: The IDLE2 sequence is enabled for baud rates of 5.0 and below.

The RapidIO II IP core currently supports only the IDLE2 sequence, so

this bit always has the value of 1.

1'b1