Altera RapidIO II MegaCore Function User Manual

Page 57

Chapter 4: Functional Description

4–15

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

Table 4–7

lists the write-request conversions the RapidIO II IP core performs for

RapidIO write request packets with wrsize value less than 4’b1100.

1001

0

0

1

0000_0000_1111_1100

1

1

1111_1100_0000_0000

1

0

1

0000_0000_0011_1111

1

1

0011_1111_0000_0000

1010

0

0

1

0000_0000_1111_1110

1

1

0000_0000_0111_1111

1

0

1

1111_1110_0000_0000

1

1

0111_1111_0000_0000

1011

0

0

1

0000_0000_1111_1111

1

1

1111_1111_0000_0000

1

0

1

1111_1111_1111_1111

1

1100

0

0

2

1111_1111_1111_1111

1

0

4

1111_1111_1111_1111

1101

0

0

6

1111_1111_1111_1111

1

0

8

1111_1111_1111_1111

1110

0

0

10

1111_1111_1111_1111

1

0

12

1111_1111_1111_1111

1111

0

0

14

1111_1111_1111_1111

1

0

16

1111_1111_1111_1111

Notes to

(1) The RapidIO link partner should avoid read requests with this rdsize value, because the resulting byteenable

value is not allowed by the Avalon-MM specification. However, if the RapidIO II IP core receives a read request with

this rdsize value, the IP core issues these transactions on the I/O Logical layer Avalon-MM master interface with

the illegal byteenable values, to support systems in which user logic handles these byteenable values.

(2) This combination of wdptr and rdsize values is reserved. If the RapidIO II IP core receives this combination, it

sets the Unsupported Transaction bit (UNSUPPORT_TRAN) in the Logical/Transport Layer Error Detect

CSR (

) and returns an ERROR response.

(3) If rdsize has a value greater than 4’b1011, and address[0] has the value of 1, the RapidIO II IP core sets the

Unsupported Transaction bit (UNSUPPORT_TRAN) in the Logical/Transport Layer Error Detect CSR

(

) and returns an ERROR response.

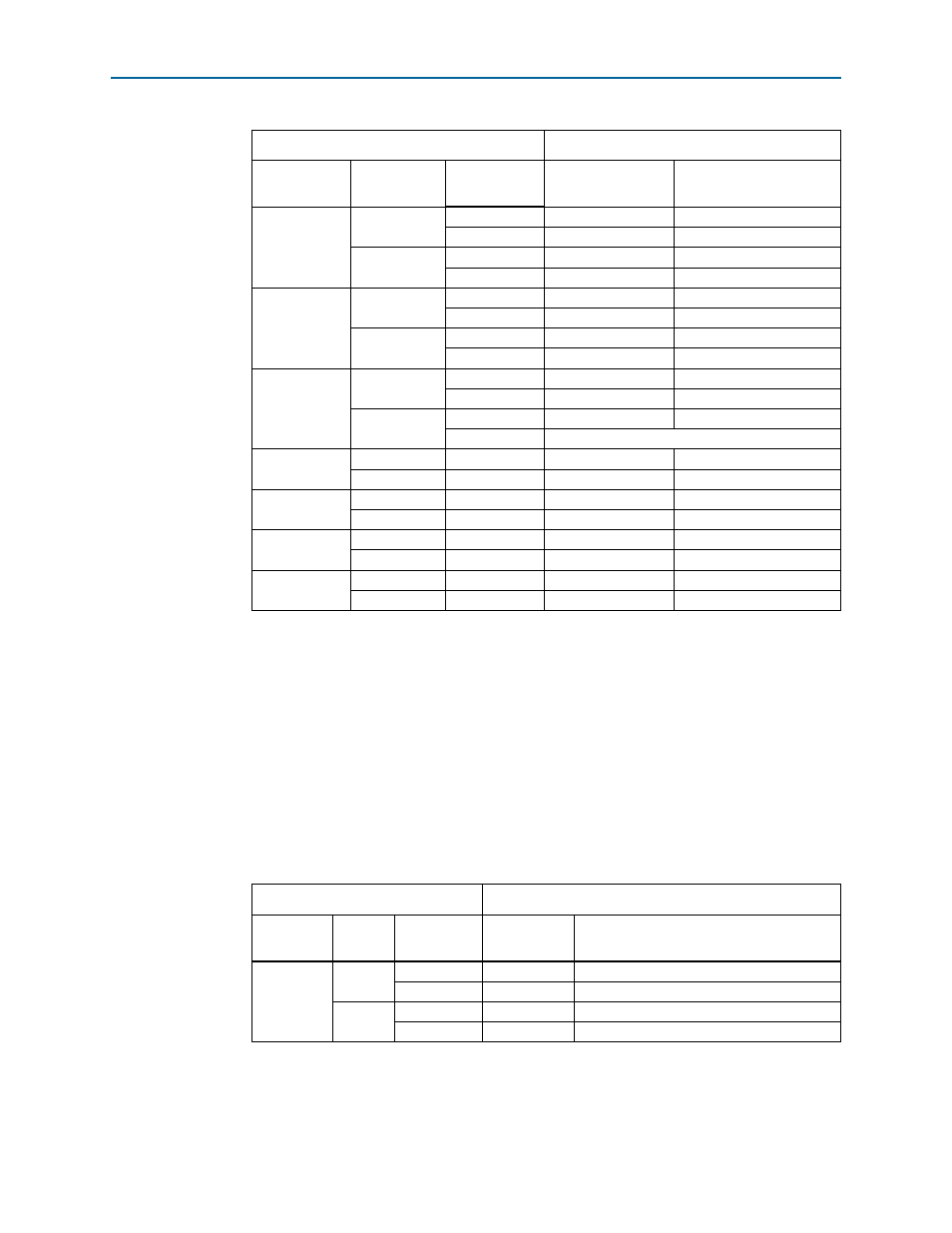

Table 4–7. Avalon-MM I/O Master Write Transaction Burstcount and Byteenable I (Part 1 of 3)

RapidIO Field Values

Avalon-MM Signal Values

wrsize

(4'bxxxx)

wdptr

(1'bx)

address[0]

(1'bx)

Burstcount

Byteenable (16'bxxxx_xxxx_xxxx_xxxx)

0000

0

0

1

0000_0000_1000_0000

1

1

1000_0000_0000_0000

1

0

1

0000_0000_0000_1000

1

1

0000_1000_0000_0000

Table 4–6. Avalon-MM I/O Master Read Transaction Burstcount (Part 2 of 2)

RapidIO Field Values

Avalon-MM Signal Values

rdsize

(4'bxxxx)

wdptr

(1'bx)

address[0]

(1'bx)

Burstcount

Byteenable

(16'bxxxxxxxxxxxxxxxx)