Altera RapidIO II MegaCore Function User Manual

Page 55

Chapter 4: Functional Description

4–13

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

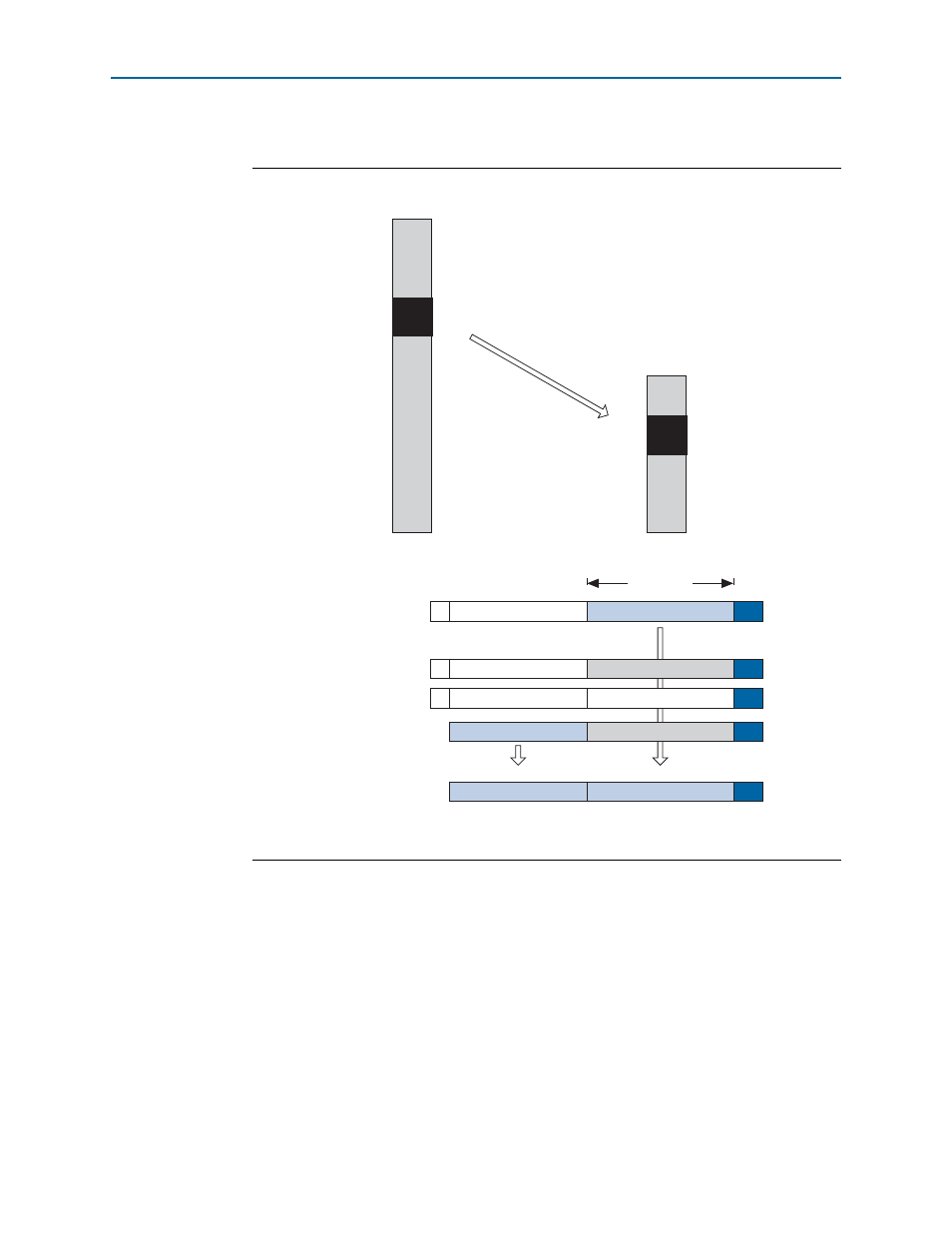

shows a block diagram of the I/O master‘s window translation.

RapidIO Packet Data wdptr and Data Size Encoding in Avalon-MM

Transactions

The RapidIO II IP core converts RapidIO packets to Avalon-MM transactions. The

RapidIO packets’ read size, write size, and word pointer fields, and the least

significant bit of the address field, are translated to the Avalon-MM burst count and

byteenable values.

Figure 4–5. I/O Master Window Translation

Note to

:

(1) These bits must have the same value in the initial RapidIO address and in the window base.

Initial

RapidIO Address

0x00000000

0x000000000

Base

Offset

Window

0xFFFFFFF8

0x3FFFFFFF8

Don’t Care

Don’t Care

33

Window Base

Window Mask

Window Offset

Resulting

Avalon-MM Address

0

3

4

0

3

4

31

31

XAMB

XAMM

(1)

(1)

Avalon-MM

Address Space

RapidIO

Address Space

Window Size

11111111.........................11

11

000000000000000..............00