Altera RapidIO II MegaCore Function User Manual

Page 166

6–28

Chapter 6: Software Interface

Transport and Logical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

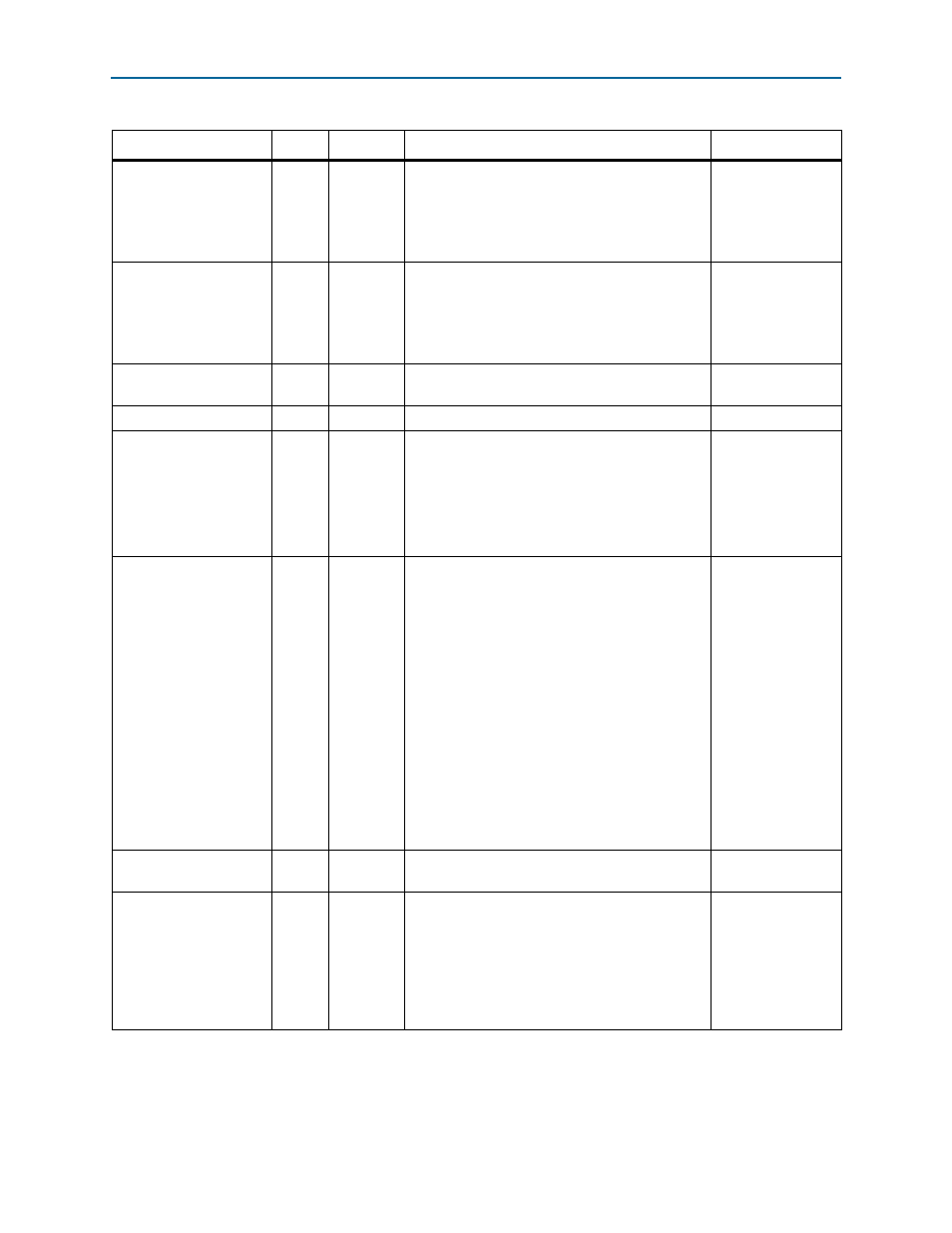

User Guide

Extended route

table configuration

support

[9]

RO

Processing element supports extended route table

configuration mechanism.

This property is relevant in switch processing

elements only. In non-switch processing elements,

it is ignored.

Standard route

table configuration

support

[8]

RO

Processing element supports standard route table

configuration mechanism.

This property is relevant in switch processing

elements only. In non-switch processing elements,

it is ignored.

Flow Control

Support

[7]

RO

Processing element supports flow control

extensions.

RSRV

[6]

RO

Reserved

1'h0

CRF Support

[5]

RO

Processing element supports the Critical Request

Flow (CRF) indicator:

1'b0—Processing element does not support

Critical Request Flow

1'b1—Processing element supports Critical

Request Flow

1'b1

LARGE_TRANSPORT

[4]

RO

Processing element supports common transport

large systems:

1'b0—Processing element does not support

common transport large systems (processing

element requires that the device ID width be 8

bits, and does not support a device ID width of

16 bits).

1'b1—Processing element supports common

transport large systems (processing element

supports a device ID width of 16 bits).

The value of this field is determined by the device

ID width you select in the RapidIO II parameter

editor with the Enable 16-bit device ID width

setting. Refer to

.

Extended features

[3]

RO

Processing element has extended features list; the

extended features pointer is valid.

1'b1

Extended addressing

support

[2:0]

RO

Indicates the number of address bits supported by

the processing element, both as a source and

target of an operation. All processing elements

support a minimum 34-bit address. The RapidIO II

IP core supports the following valid value:

3'b001—Processing element supports 34-bit

addresses

3'b001

Note to

:

(1) The value is set in the RapidIO II parameter editor.

(2) If the Standard route table configuration support bit or the Extended route table configuration support bit is set, user logic must implement

the functionality and registers to support the standard or extended route table configuration. The RapidIO II IP core does not implement the

Standard Route CSRs at offsets 0x70, 0x74, and 0x78.

Table 6–26. Processing Element Features CAR—Offset: 0x10 (Part 2 of 2)

Field

Bits

Access

Function

Default