Altera RapidIO II MegaCore Function User Manual

Page 109

Chapter 4: Functional Description

4–67

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

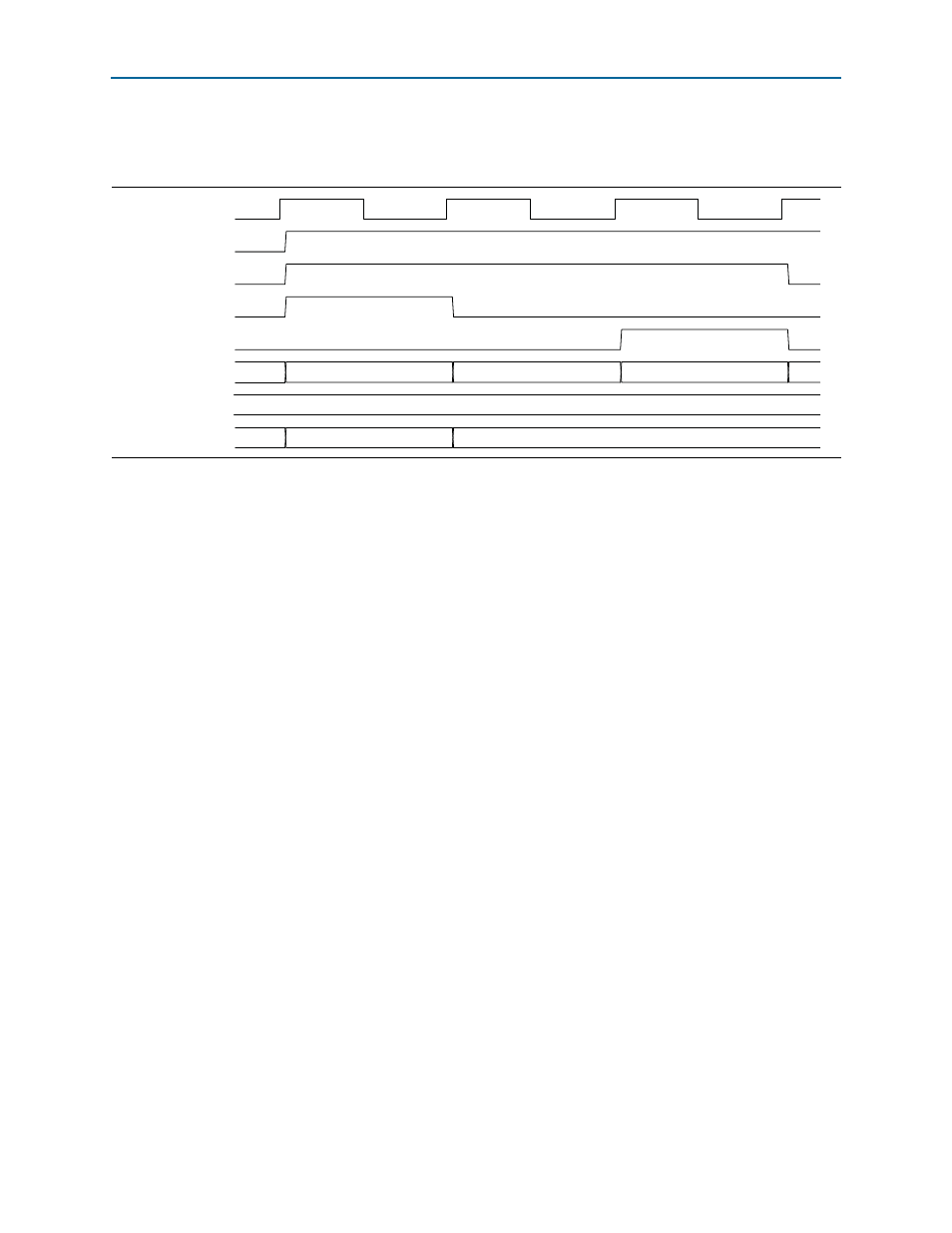

Figure 4–25

shows the behavior of the signals on the Avalon-ST pass-through

interface for this example transaction.

In the first clock cycle of the example, the IP core asserts gen_tx_ready to indicate it is

ready to sample data. In the same cycle, user logic asserts gen_tx_valid. Because both

gen_tx_ready

and gen_tx_valid are asserted, this clock cycle is an Avalon-ST ready

cycle. The user logic provides valid data on gen_tx_data for the IP core to sample, and

asserts gen_tx_startofpacket to indicate the current value of gen_tx_data is the

initial piece of the current packet (the start of packet). On gen_tx_packet_size, user

logic reports the full length of the packet is 0x30, which is decimal 48, because the

packet comprises eight bytes of header and 40 bytes of payload data.

The user logic provides the 40-byte payload and 8-byte header on the same bus,

gen_tx_data[127:0]

. Transferring these 48 bytes of information requires three clock

cycles. During all of these cycles, the IP core holds gen_tx_ready high and user logic

holds gen_tx_valid high, indicating the cycles are all Avalon-ST ready cycles. In the

second cycle, user logic holds gen_tx_startofpacket and gen_tx_endofpacket low,

because the information on gen_tx_data is neither start of packet nor end of packet

data. In the third clock cycle, user logic asserts gen_tx_endofpacket and sets

gen_tx_empty

to the value of 0x0 to indicate that all of the bytes of data available on

gen_tx_data

in the current clock cycle are valid.

In this example, the IP core does not deassert gen_tx_ready following the three ready

cycles, indicating that it is ready to accept an additional transaction whenever user

logic is ready to send an additional transaction. Whether or not the IP core deasserts

gen_tx_ready

following the three Avalon-ST ready cycles, the next cycle is not a ready

cycle, because user logic has deasserted gen_tx_valid.

Figure 4–25. Avalon-ST Pass-Through Interface SWRITE Transmit Example

clk

gen_tx_ready

gen_tx_valid

gen_tx_startofpacket

gen_tx_endofpacket

00C6DDAA0AABBCC8FFFEFDFCFBFAF9F8

F7F6F5F4F3F2F1F0EFEEEDECEBEAE9E8

E7E6E5E4E3E2E1E0DFDEDDDCDBDAD9D8

030

0

gen_tx_data[127:0]

gen_tx_empty[3:0]

gen_tx_packet_size[8:0]