Table 6–8 on, Table 6–8 – Altera RapidIO II MegaCore Function User Manual

Page 146

6–8

Chapter 6: Software Interface

Physical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

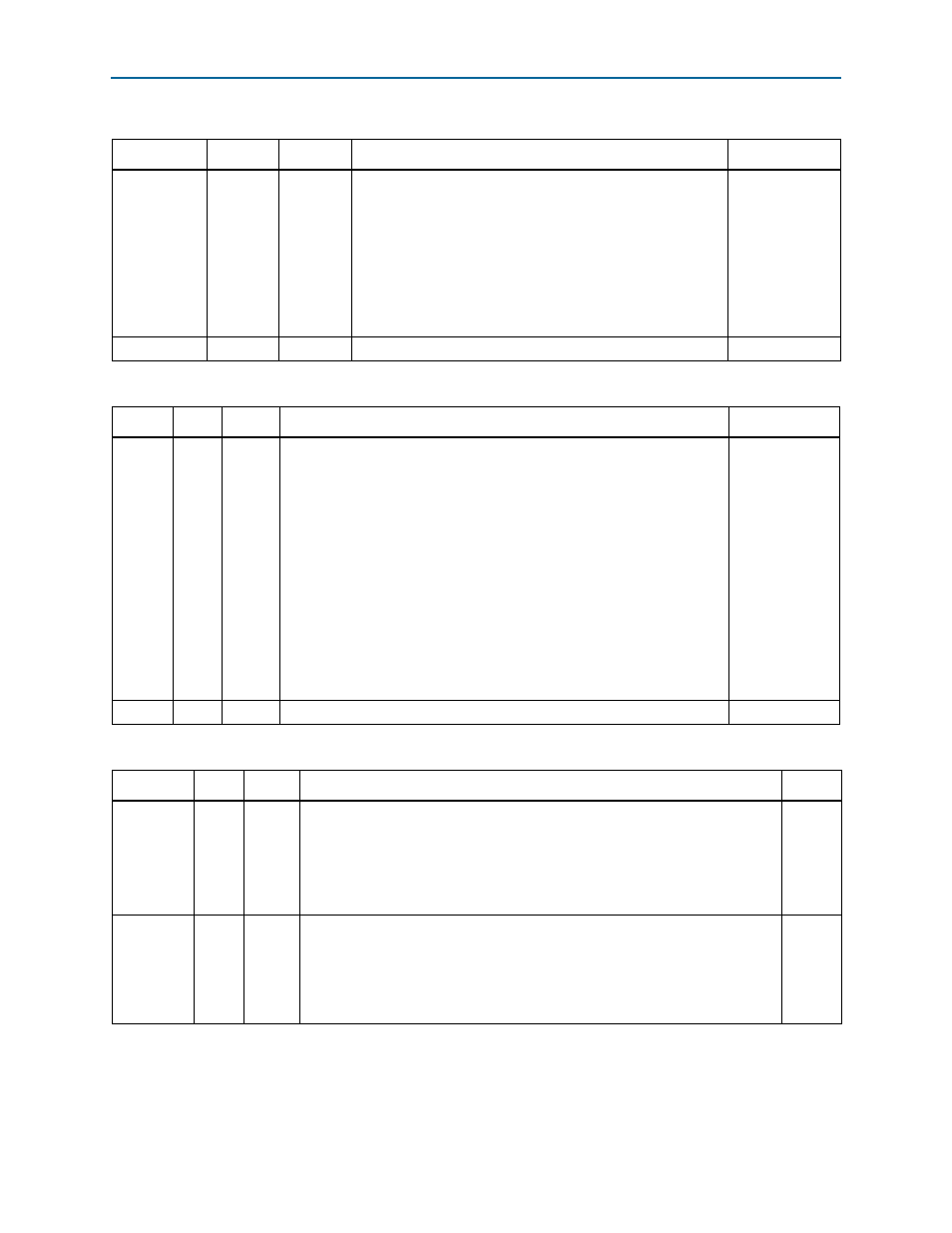

Table 6–7. Port Link Time-Out Control CSR—0x120

Field Bits

Access

Function

Default

VALUE

[31:8] RW

Time-out interval value for link-layer event pairs such as the

time interval between sending a packet and receiving the

corresponding acknowledge control symbol, or between

sending a link-request and receiving the corresponding

link-response.

The duration of the link-response time-out is approximately

equal to 4.5 seconds multiplied by the contents of this field,

divided by (2

24

- 1).

24'hFF_FFFF

RSRV

[7:0] UR0

Reserved

8’h0

Table 6–8. Port Response Time-Out Control CSR—0x124

Field Bits

Access

Function

Default

VALUE

[31:8] RW

Time-out internal value for request-response pairs: the time interval

between sending a request packet and receiving the corresponding

response packet.

The duration of the port response time-out for all transactions that require a

response—including MAINTENANCE, DOORBELL, NWRITE_R, and NREAD

transactions—is approximately equal to 4.5 seconds multiplied by the

contents of this field, divided by (2

24

- 1).

Note: A new value in this field might not propagate quickly enough to be

applied to the next transaction.

Note: Avoid changing the value in this field when any packet is waiting to be

transmitted or waiting for a response, to ensure that in each FIFO, the

pending entries all have the same time-out value.

24'hFF_FFFF

RSRV

[7:0] UR0

Reserved

8'h0

Table 6–9. Port General Control—Offset: 0x13C (Part 1 of 2)

Field

Bits

Access

Function

Default

HOST

[31]

RW

A host device is a device that is responsible for system exploration, initialization,

and maintenance. Host devices typically initialize agent or slave devices.

1'b0 - agent or slave device

1'b1 - host device

This field is for software use only. Its value has no effect on hardware.

ENA

[30]

RW

The Master Enable bit controls whether or not a device is allowed to issue

requests to the system. If Master Enable is not set, the device may only

respond to requests.

1'b0 - The processing element cannot issue requests

1'b1 - The processing element can issue requests