Altera RapidIO II MegaCore Function User Manual

Page 154

6–16

Chapter 6: Software Interface

Physical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

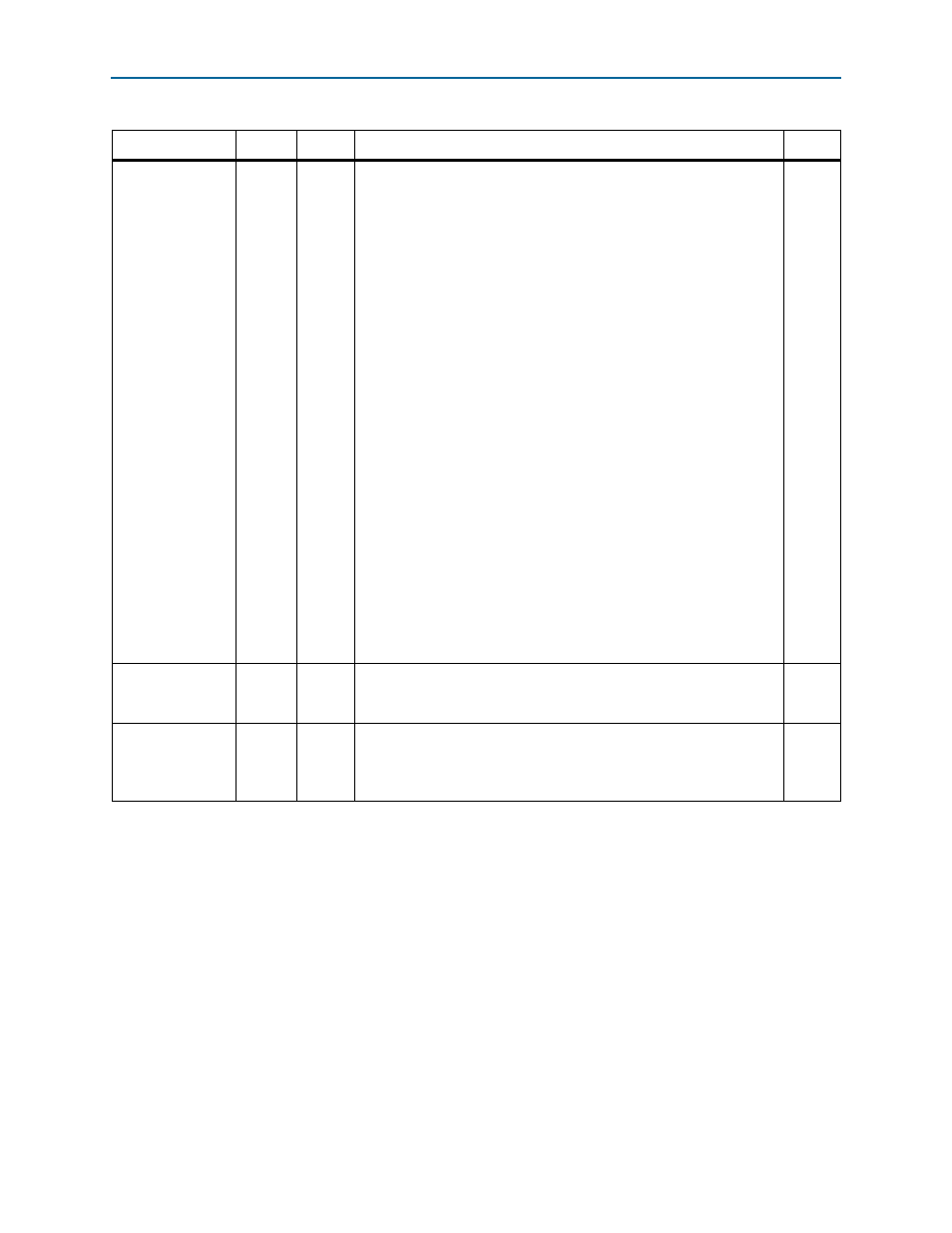

PORT_ERR

[2]

RW1C

This bit is set if the input port error recovery state machine encounters

an unrecoverable error or the output port error recovery state machine

enters the fatal_error state.

The input port error recovery state machine encounters an

unrecoverable error if it times out while waiting for a link-request

after sending a packet-not-accepted control symbol.

The output port error recovery state machine enters the fatal_error state

if the following sequence of events occurs:

1. The output port error recovery state machine enters the stop_output

state when it receives a packet-not-accepted control symbol. In

response, it sends the

input-status

link-request/input-status (restart-from-error)

control symbol.

2. One of the following events occurs in response to the link-request

control symbol:

■

If the link-response is received but the ackID is outside of the

outstanding ackID set, then the output port error recovery state

machine enters the fatal_error state.

■

If the port times out before receiving link-response, for seven

attempts to send a link-request, then the output port error

recovery state machine enters the fatal_error state.

When the PORT_ERR bit is set, software determines the behavior of the

RapidIO II IP core, as described in

. After it

is set, this bit is cleared only when software writes the value of 1 to it.

The port_error output signal mirrors this register bit.

1'b0

PORT_OK

[1]

RO

Input and output ports are initialized and can communicate with the

adjacent device. This bit is asserted when the link is initialized. The value

in this field appears on the port_ok output signal.

1'b0

PORT_UNINIT

[0]

RO

Input and output ports are not initialized and are in training mode. This

bit and the PORT_OK bit are mutually exclusive: at any time, at most one

of them can be asserted. The RapidIO II IP core deasserts this bit when

the port is initialized.

1'b1

Note to

:

(1) Refer to

“Error Detection and Management” on page 4–76

for details.

Table 6–14. Port 0 Error and Status CSR—Offset: 0x158

(1)

(Part 5 of 5)

Field

Bits

Access

Function

Default