Error reporting signals, Error reporting signals –13, Table 5–16 – Altera RapidIO II MegaCore Function User Manual

Page 137

Chapter 5: Signals

5–13

Error Management Extension Signals

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

Error Reporting Signals

lists the Error Management Extensions error reporting signals.

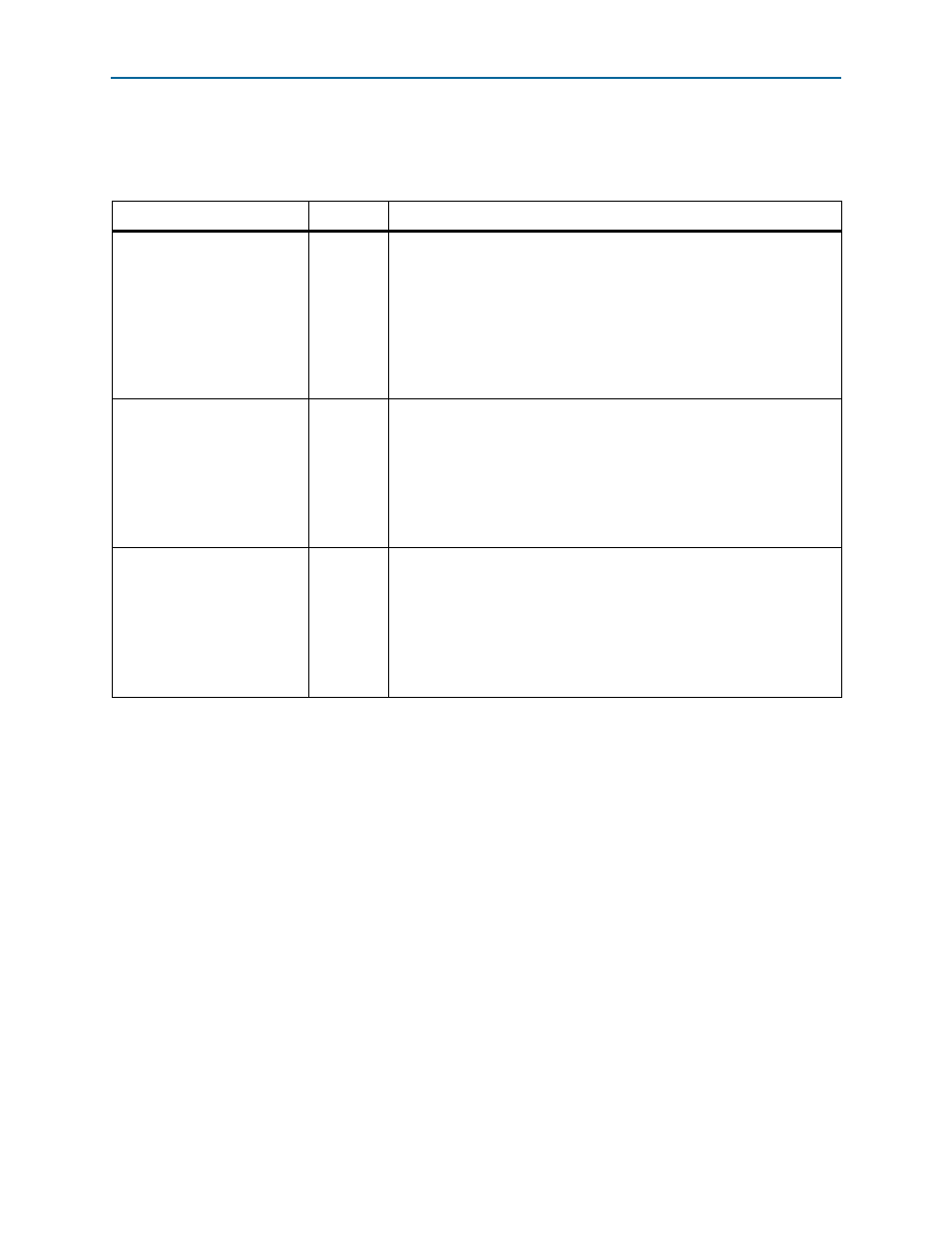

Table 5–16. Error Management Extensions Error Reporting Signals

Signal

Direction

Description

logical_transport_error

Output

Asserted when an error is logged in the Logical/Transport Layer

Error Detect

CSR (

), and this error is enabled

for reporting in the Logical/Transport Layer Error Enable CSR

(

). If the LOG_TRANS_ERR_IRQ_EN bit in the Port

0 Control

CSR at offset 0x15C (

) has the value of

1’b1 when this signal is raised, the RapidIO II IP core asserts the

std_reg_mnt_irq

interrupt signal. This signal remains asserted until the

Logical/Transport Layer Error Detect

CSR is unlocked by user

logic writing the value of 0 to the register.

port_failed

Output

This signal is available to report link status to the system host. The signal is

asserted when the Error Rate Failed Threshold trigger

(ERR_RATE_FAILED_THRESHOLD field of the Port 0 Error Rate

Threshold

) is enabled (is

non-zero) and this value is reached. If the PORT_FAIL_IRQ_EN bit in the

Port 0 Control

) has the

value of 1’b1 when this signal is raised, the RapidIO II IP core asserts the

std_reg_mnt_irq

interrupt signal.

port_degraded

Output

This signal is available to report link status to the system host. The signal is

asserted when the Error Rate Degraded Threshold trigger

(ERR_RATE_DEGR_THRESHOLD field of the Port 0 Error Rate

Threshold

) is enabled (is

non-zero) and this value is reached. If the PORT_DEGR_IRQ_EN bit in the

Port 0 Control

) has the

value of 1’b1 when this signal is raised, the RapidIO II IP core asserts the

std_reg_mnt_irq

interrupt signal.