Altera RapidIO II MegaCore Function User Manual

Page 156

6–18

Chapter 6: Software Interface

Physical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

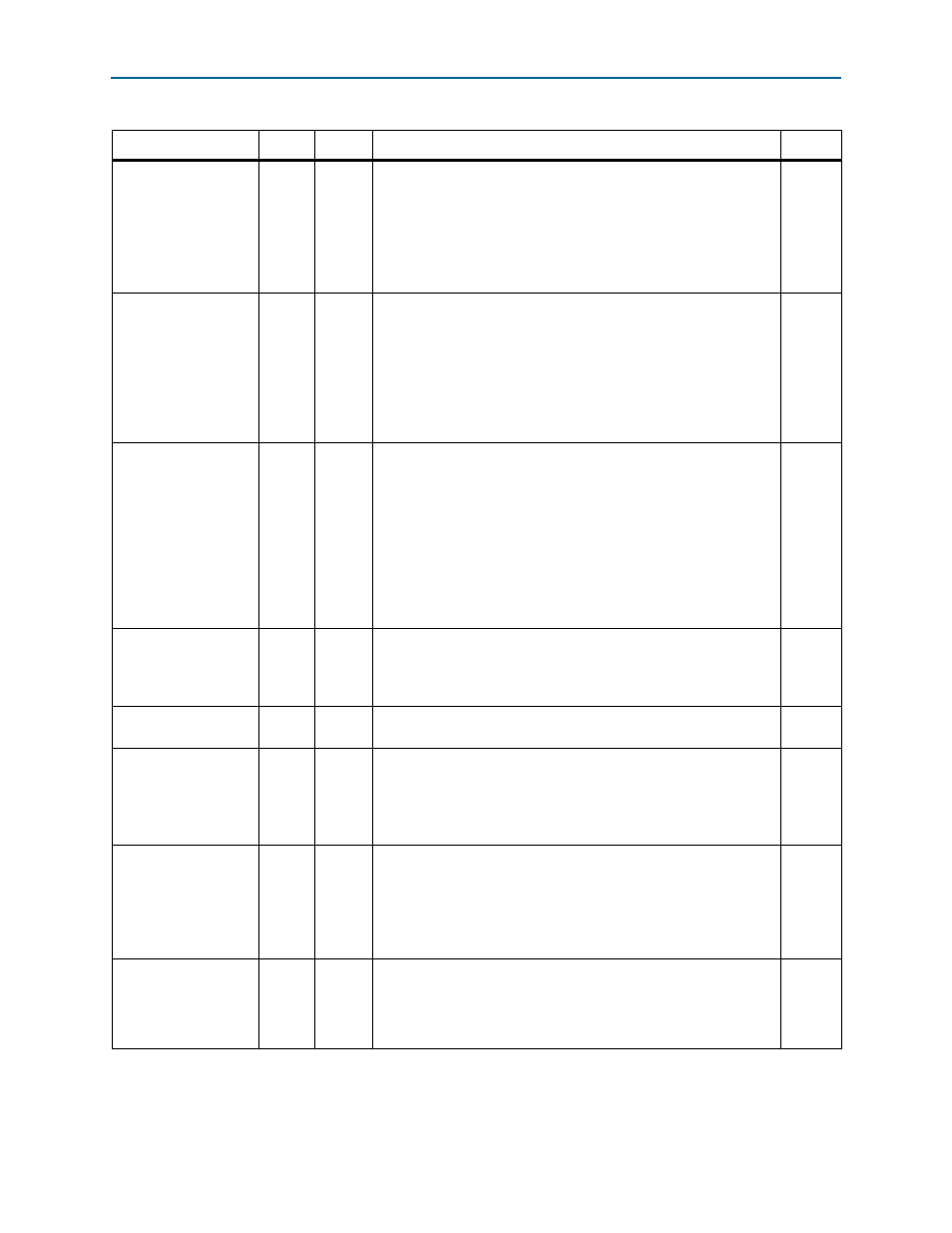

PORT_DIS

[23]

RW

Port disable:

'b0—Port receivers/drivers are enabled.

'b1—Port receivers are disabled and are unable to receive or

transmit any packets or control symbols.

While this bit is set, the initialization state machines’ force_reinit

signal is asserted. This assertion forces the port to the SILENT state

1'b0

OUT_PENA

[22]

RW

Output port transmit enable:

'b0—Port is stopped and not enabled to issue any packets except

to route or respond to I/O logical MAINTENANCE packets. Control

symbols are not affected and are sent normally.

'b1—Port is enabled to issue packets.

The value in the PORT_LOCKOUT field (bit [1] of this register) can

override the values in the OUT_PENA and IN_PENA fields

1'b0

IN_PENA

[21]

RW

Input port receive enable:

'b0—Port is stopped and only enabled to respond to I/O Logical

MAINTENANCE

requests. Other requests return packet-not-

accepted

control symbols to force an error condition to be

signaled by the sending device. However, the IP core still handles

normally any control symbols it receives.

'b1—Port is enabled to respond to any packet.

The value in the PORT_LOCKOUT field (bit [1] of this register) can

override the values in the OUT_PENA and IN_PENA fields.

1'b0

ERR_CHK_DIS

[20]

RO

This bit enables (1’b0) or disables (1’b1) all RapidIO transmission

error checking. The RapidIO II IP core does not support the

disabling of error checking and recovery, so this bit always has the

value of 1’b0.

1'b0

Multicast-event

Participant

[19]

RW

Indicates that the system should send incoming Multicast-event

control symbols to this port (multiple port devices only).

1'b1

Flow Control

Participant

[18]

RW

Enables or disables flow control transactions:

1’b0: Do not route or issue flow control transactions to this port

1’b1: Route or issue flow control transactions to this port.

This field does not affect the IP core configuration.

Enumeration

Boundary

[17]

RW

Indicates whether this port should delimit enumeration. Any

enumeration boundary aware system enumeration algorithm should

honor this flag. The algorithm, on either the Rx port or the Tx port,

should not enumerate past a port in which this bit is set to the value

of 1’b1. This field supports software-enforced enumeration domains

in the RapidIO network.

Flow Arbitration

Participant

[16]

RW

Enables or disables flow arbitration transactions:

1’b0: Do not route or issue flow arbitration transactions to this

port

1’b1: Route or issue flow arbitration transactions to this port.

Table 6–15. Port 0 Control CSR—Offset: 0x15C (Part 2 of 4)

Field

Bits

Access

Function

Default