Signals, Global signals, Chapter 5. signals – Altera RapidIO II MegaCore Function User Manual

Page 125: Global signals –1, Chapter 5

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

5. Signals

This chapter lists the RapidIO II IP core signals.

Signals are listed with their widths. In this context, the n in [n:0] is the number of

lanes minus one, so that signal[n:0] has one bit for each lane.

Global Signals

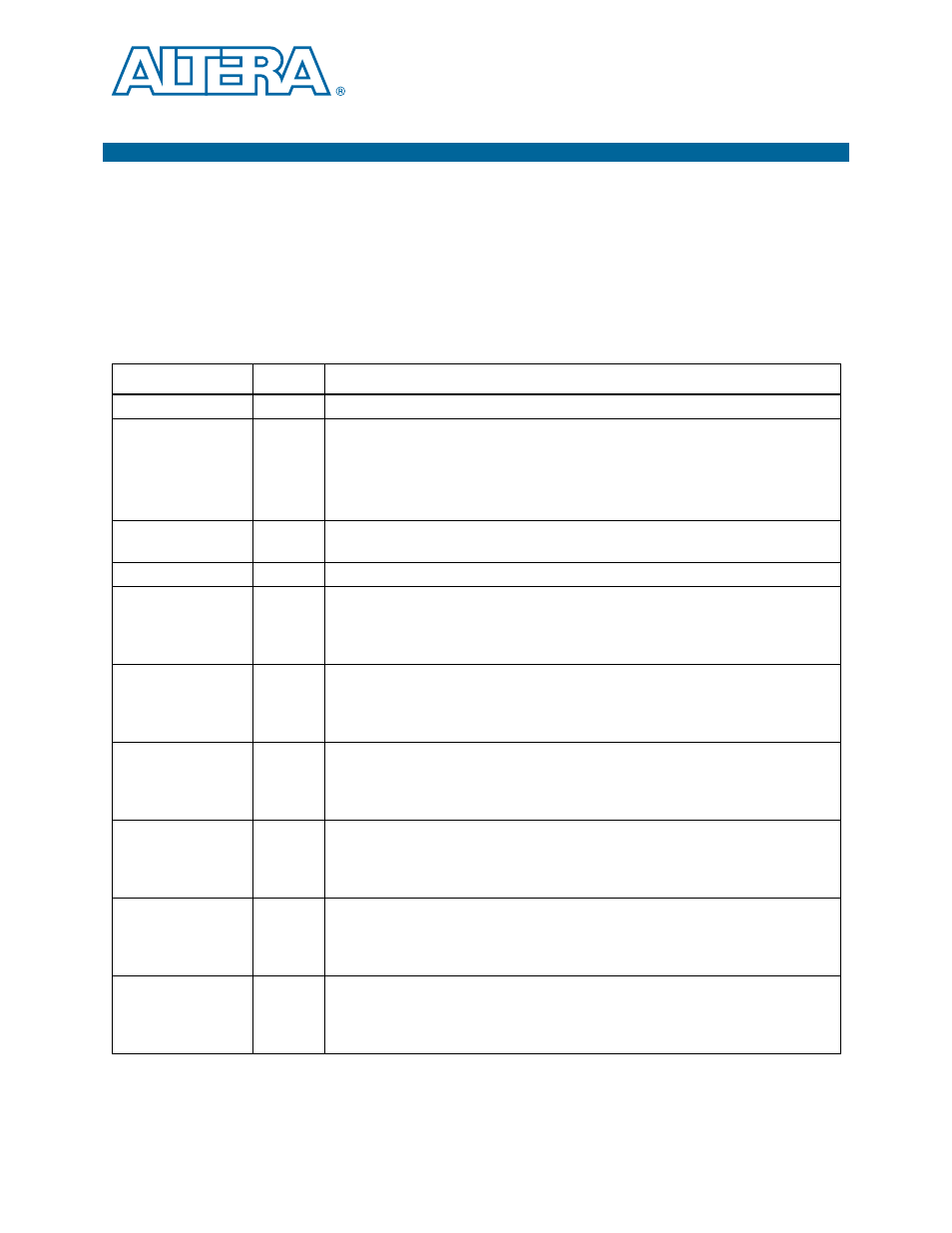

Table 5–1. Clock Signals (Part 1 of 2)

Signal

Direction

Description

sys_clk

Input

Avalon system clock.

tx_pll_refclk

Input

Physical layer reference clock. Your design must drive this clock from the same source

as the sys_clk input clock.

In Arria 10 variations, despite the signal name, this clock is the reference clock for the

RX CDR block in the transceiver. In other variations, this clock is also the reference

clock for the TX PLL in the transceiver.

rx_clkout

Output

Receive-side recovered clock. This signal is derived from the incoming RapidIO data.

Refer to

“Recovered Data Clock” on page 4–4

tx_clkout

Output

Transmit-side clock.

tx_bonding_clocks

_ch0[5:0]

Input

Transceiver channel TX input clocks for RapidIO lane 0. This signal is available only in

Arria 10 variations. Each transceiver channel that corresponds to a RapidIO lane has

six input clock bits. The bits are expected to be driven from a TX PLL. Refer to

“External Transceiver PLL” on page 2–8

tx_bonding_clocks

_ch1[5:0]

Input

Transceiver channel TX input clocks for RapidIO lane 0. This signal is available only in

Arria 10 2x and 4x variations. Each transceiver channel that corresponds to a RapidIO

lane has six input clock bits. The bits are expected to be driven from a TX PLL. Refer to

“External Transceiver PLL” on page 2–8

tx_bonding_clocks

_ch2[5:0]

Input

Transceiver channel TX input clocks for RapidIO lane 0. This signal is available only in

Arria 10 4x variations. Each transceiver channel that corresponds to a RapidIO lane has

six input clock bits. The bits are expected to be driven from a TX PLL. Refer to

“External Transceiver PLL” on page 2–8

tx_bonding_clocks

_ch3[5:0]

Input

Transceiver channel TX input clocks for RapidIO lane 0. This signal is available only in

Arria 10 4x variations. Each transceiver channel that corresponds to a RapidIO lane has

six input clock bits. The bits are expected to be driven from a TX PLL. Refer to

“External Transceiver PLL” on page 2–8

reconfig_clk_ch0

Input

Clocks the Arria 10 dynamic reconfiguration interface for RapidIO lane 0. This interface

is available in Arria 10 variations for which you turn on

Enable transceiver

dynamic reconfiguration

. The allowed frequency range for this clock is defined in

the

.

reconfig_clk_ch1

Input

Clocks the Arria 10 dynamic reconfiguration interface for RapidIO lane 1. This interface

is available in Arria 10 2x and 4x variations for which you turn on

Enable

transceiver dynamic reconfiguration

. The allowed frequency range for this

cl