Error management registers, Error management registers –42, Error – Altera RapidIO II MegaCore Function User Manual

Page 180

6–42

Chapter 6: Software Interface

Transport and Logical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

Error Management Registers

The RapidIO II IP core implements the Error Management Extensions registers. These

registers are configured in your RapidIO II IP core variation if you turn on Enable

error management extension registers

on the Error Management Registers tab of the

RapidIO II parameter editor.

shows the memory map for the RapidIO II IP core error management

registers. The offset values within the address space for these registers are defined by

the RapidIO standard.

through

describe the error management registers. These

registers can be used by software to diagnose problems with packets that are received

by the local endpoint. If enabled, the detected error triggers the assertion of

std_reg_mnt_irq

. Information about the packet that caused the error is captured in

the capture registers. After an error condition is detected, the information is captured

and the capture registers are locked until the Error Detect CSR is cleared. Upon being

cleared, the capture registers are ready to capture a new packet that exhibits an error

condition.

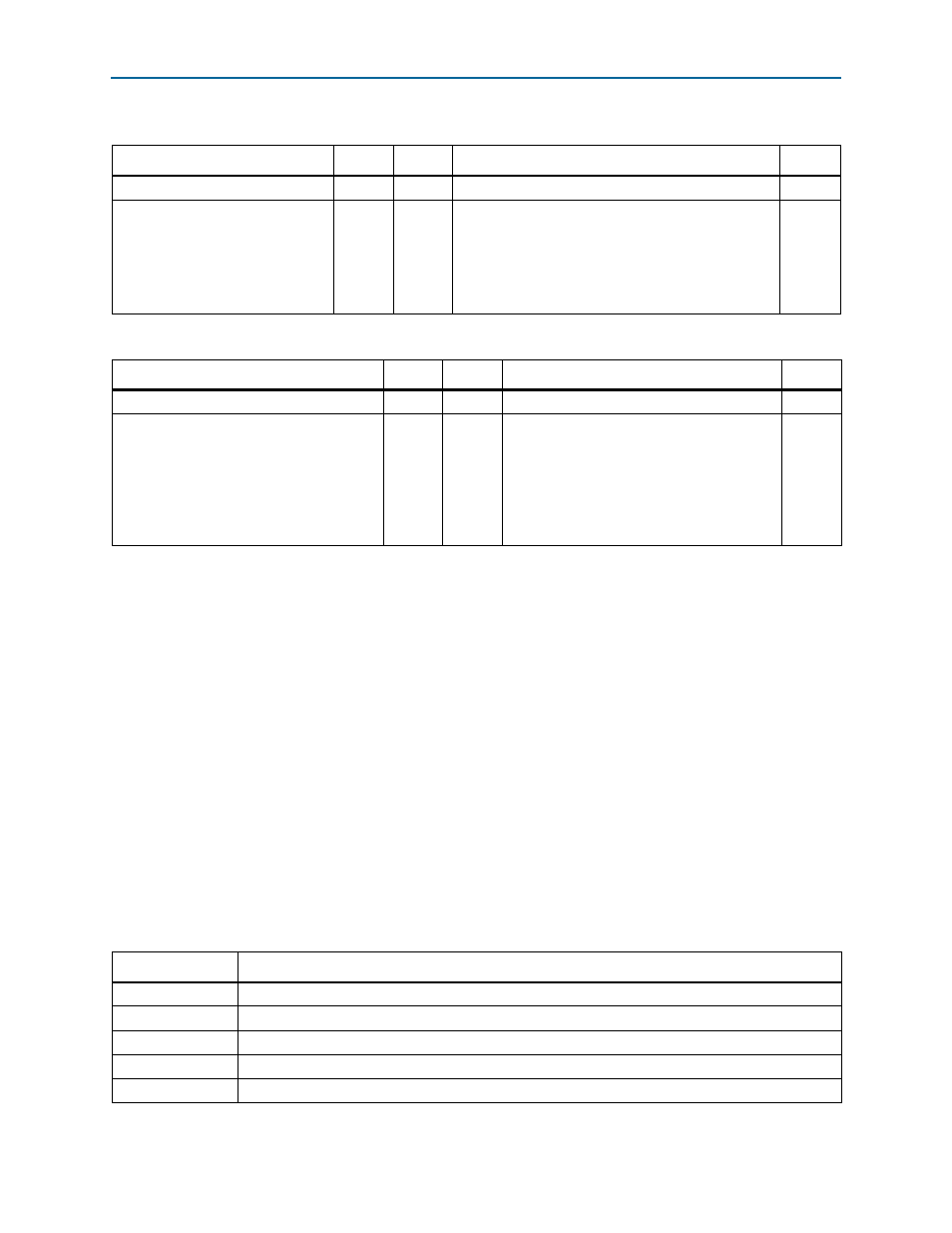

Table 6–63. Input/Output Slave Avalon-MM Write Transactions—Offset: 0x1050C

Field

Bits

Access

Function

Default

RSRV

[31:16]

RO

Reserved

16'h0

STARTED_WRITES

[15:0]

RO

Number of write transfers initiated on Avalon-MM

Input/Output Slave port so far. Count increments on

first system clock cycle in which the io_s_write

signal is asserted and the io_s_wr_waitrequest

signal is not asserted. This counter rolls over to 0 after

its maximum value.

16'b0

Table 6–64. Input/Output Slave RapidIO Write Requests—Offset: 0x10510

Field

Bits

Access

Function

Default

RSRV

[31:16]

RO

Reserved

16'h0

COMPLETED_OR_CANCELLED_WRITES

[15:0]

RO

Number of write-request packets transferred

from the Avalon-MM Input/Output Slave

module to the Transport layer or cancelled.

Count increments when the write-request

packet is sent to the Transport layer, or when

a write transaction is cancelled. This counter

rolls over to 0 after its maximum value.

16'b0

Table 6–65. Error Management Extensions Register Map (Part 1 of 2)

Address

Name

0x300

Error Management Extensions Block Header

0x308

Logical/Transport

Layer Error Detect

0x30C

Logical/Transport

Layer Error Enable

0x314

Logical/Transport

Layer Address Capture

0x318

Logical/Transport

Layer Device ID Capture