Refer to, Write, refer to – Altera RapidIO II MegaCore Function User Manual

Page 185

Chapter 6: Software Interface

6–47

Transport and Logical Layer Registers

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

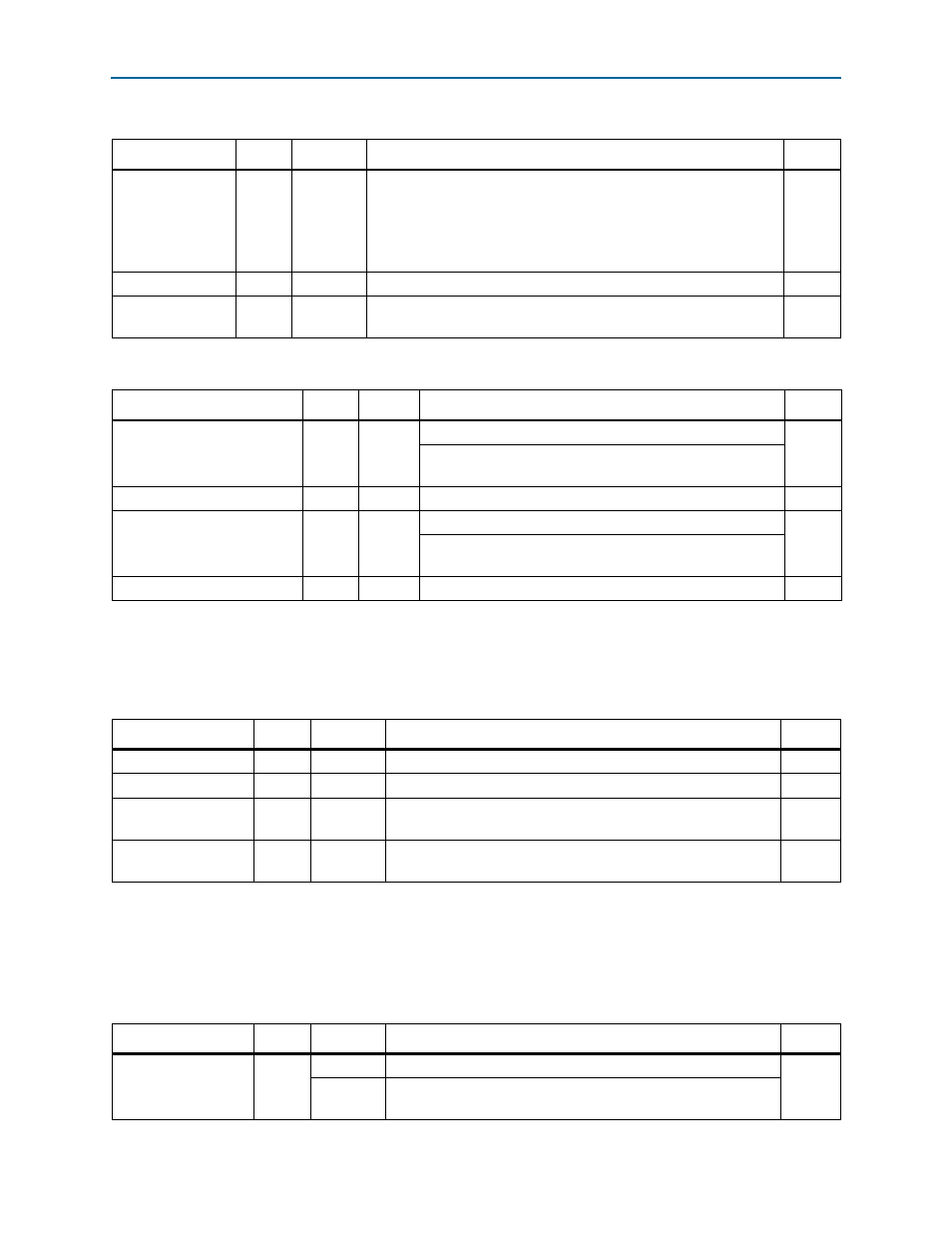

Table 6–69. Logical/Transport Layer Address Capture CSR—Offset: 0x314

Field

Bits

Access

Function

Default

ADDRESS

[31:3]

RW

Least significant 29 bits of the RapidIO address associated with the

error (for requests, for responses if available).

In the case of a Maintenance response with Error status, the IP core

sets this field to the 21-bit config_offset value from the original

request.

29'h0

RSRV

[2]

RO

Reserved

1'b0

XAMSBS

[1:0]

RW

Extended address bits of the address associated with the error (for

requests, for responses if available).

2'h0

Table 6–70. Logical/Transport Layer Device ID Capture CSR—Offset: 0x318

Field

Bits

Access

Function

Default

LARGE_DESTINATION_ID

(MSB)

[31:24] RO

Reserved if the system does not support 16-bit device ID.

8'h0

MSB of the Destination ID if the system supports 16-bit

device ID.

DESTINATION_ID

[23:16] RO

The destination ID associated with the error.

8'h0

LARGE_SOURCE_ID (MSB)

[15:8]

RO

Reserved if the system does not support 16-bit device ID.

8'h0

MSB of the Source ID if the system supports 16-bit device

ID.

SOURCE_ID

[7:0]

RO

The source ID associated with the error.

8'h0

Notes to

:

(1) For errors the RapidIO II IP core does not detect internally, set this field using the external_capture_destinationID_wr and

external_capture_destinationID_in

input signals.For errors the RapidIO II IP core does not detect internally, set this field using the

external_capture_sourceID_wr

and external_capture_sourceID_in input signals.

Table 6–71. Logical/Transport Layer Control Capture CSR—Offset: 0x31C

Field

Bits

Access

Function

Default

FTYPE

[31:28]

RO

Format type associated with the error.

4'h0

TTYPE

[27:24]

RO

Transaction type associated with the error.

4'h0

MSG_INFO

[23:16]

RO

Letter, mbox, and msgseg for the last message request received

for the mailbox that had an error.

8'h0

Implementation

Specific

[15:0]

RO

Reserved for this implementation.

16'h0

Notes to

:

(1) For errors the RapidIO II IP core does not detect internally, set this field using the capture_ftype_wr and capture_ftype_in input signals.

(2) For errors the RapidIO II IP core does not detect internally, set this field using the capture_ttype_wr and capture_ttype_in input signals.

(3) For errors the RapidIO II IP core does not detect internally, set this field using the letter_wr, mbox_wr, msgseg_wr, and xmbox_wr, and

letter_in

, mbox_in,, msgseg_in, and xmbox_in input signals.

Table 6–72. Port-Write Target Device ID CSR—Offset: 0x328 (Part 1 of 2)

Field

Bits

Access

Function

Default

deviceID_MSB

[31:24]

RO

Reserved if the system does not support 16-bit device ID.

8'h0

RW

MSB of the Maintenance port-write target device ID to report

errors to a system host, if the system supports 16-bit device ID.