Non-doorbell register access operations, Register access interface signals – Altera RapidIO II MegaCore Function User Manual

Page 50

4–8

Chapter 4: Functional Description

Logical Layer Interfaces

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

1

The Doorbell Logical layer registers are available only in RapidIO II IP core variations

that instantiate a Doorbell Logical layer module, and you must access them through

the Doorbell module's Avalon-MM slave interface.

Non-Doorbell Register Access Operations

The RapidIO II IP core registers are 32 bits wide and are accessible only on a 32-bit

(4-byte) basis. The addressing for the registers therefore increments by units of 4.

The Register Access interface supports simple reads and writes with variable latency.

The interface provides access to 32-bit words addressed by a 22-bit wide word

address, corresponding to a 24-bit wide byte address. This address space provides

access to the entire RapidIO configuration space, including any user-defined registers.

A local host can access the RapidIO II IP core registers through the Register Access

Avalon-MM slave interface.

If your RapidIO II IP core variation includes a Maintenance module, a remote host can

access the RapidIO II IP core registers by sending MAINTENANCE transactions targeted

to this local RapidIO II IP core. If the transaction is a read or write to an address in the

IP core register address range, the RapidIO II IP core routes the transaction to the

appropriate register internally. If the transaction is a read or write to an address

outside the address ranges of the Logical layer modules instantiated in the RapidIO II

IP core, the IP core routes the transaction to user logic through the Maintenance

master interface.

For information about the RapidIO II IP core registers, refer to

Register Access Interface Signals

Table 4–4

lists the signals in the Register Access interface.

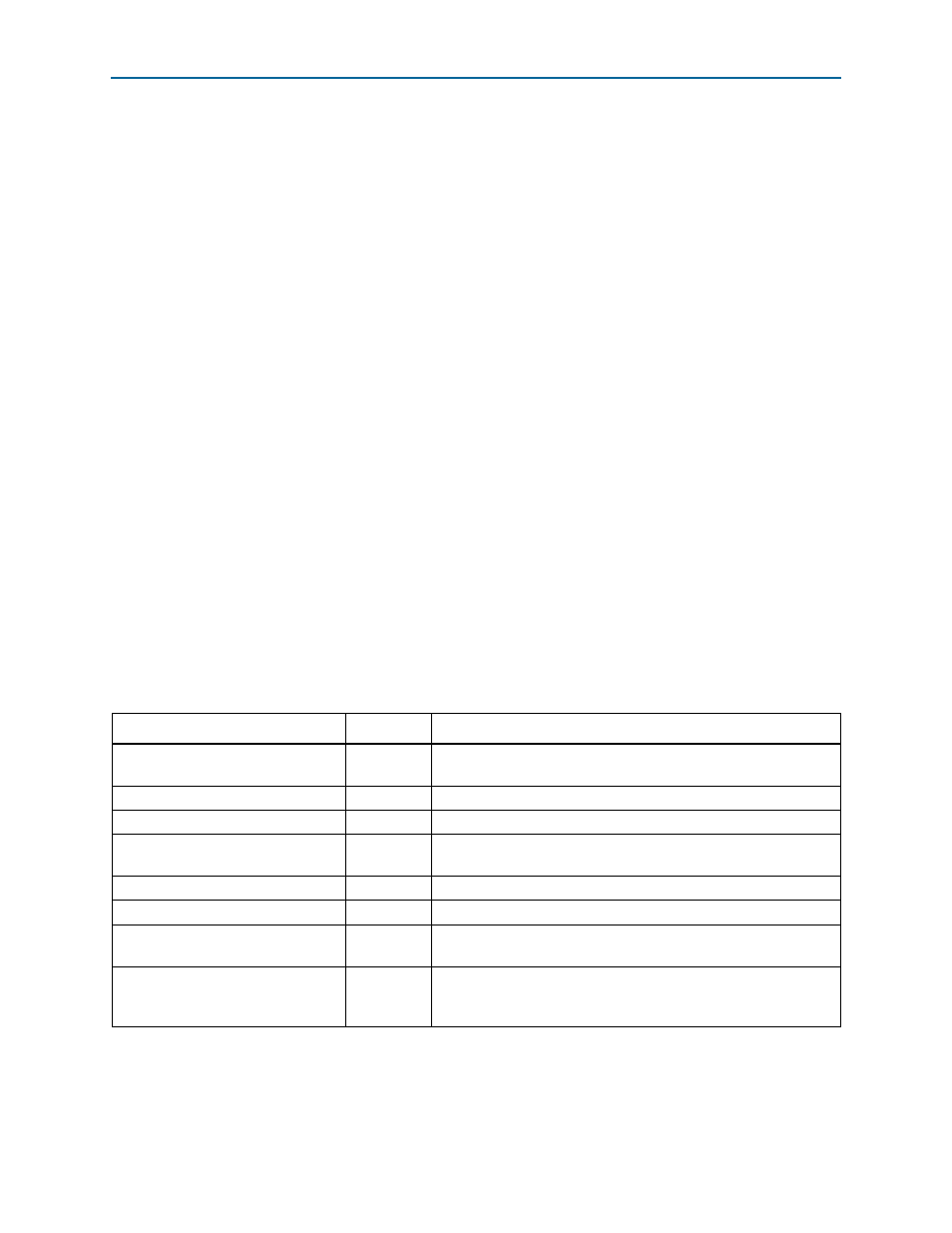

Table 4–4. Register Access Avalon-MM Slave Interface Signals (Part 1 of 2)

Signal

Direction

Description

ext_mnt_waitrequest

Output

Register Access slave wait request. The RapidIO II IP core uses this

signal to stall the requestor on the interconnect.

ext_mnt_read

Input

Register Access slave read request.

ext_mnt_write

Input

Register Access slave write request.

ext_mnt_address[21:0]

Input

Register Access slave address bus. The address is a word address,

not a byte address.

ext_mnt_writedata[31:0]

Input

Register Access slave write data bus.

ext_mnt_readdata[31:0]

Output

Register Access slave read data bus.

ext_mnt_readdatavalid

Output

Register Access slave read data valid signal supports

variable-latency, pipelined read transfers on this interface.

ext_mnt_readresponse

Output

Register Access read error, which indicates that the read transfer did

not complete successfully. This signal is valid only when the

ext_mnt_readdatavalid

signal is asserted.