Initiating read and write transactions, Initiating read and write transactions –20 – Altera RapidIO II MegaCore Function User Manual

Page 62

4–20

Chapter 4: Functional Description

Logical Layer Interfaces

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

Input/Output Avalon-MM Slave Signals

lists the Input/Output Avalon-MM Slave module interface signals.

The I/O Avalon-MM Slave module supports an interrupt line, io_s_mnt_irq, on the

Register Access interface. When enabled, the following interrupts assert the

io_s_mnt_irq

signal:

The interface supports an interrupt line, io_s_mnt_irq. When enabled, the following

interrupts assert the io_s_mnt_irq signal:

■

Read out of bounds

■

Write out of bounds

■

Invalid write

■

Invalid read or write burstcount

■

Invalid read or write byteenable value

For more information about the I/O Logical layer Avalon-MM slave module

interrupts, refer to

.

Initiating Read and Write Transactions

To initiate a read or write transaction on the RapidIO link, your system sends a read or

write request to the I/O Logical layer Slave module Avalon-MM interface.

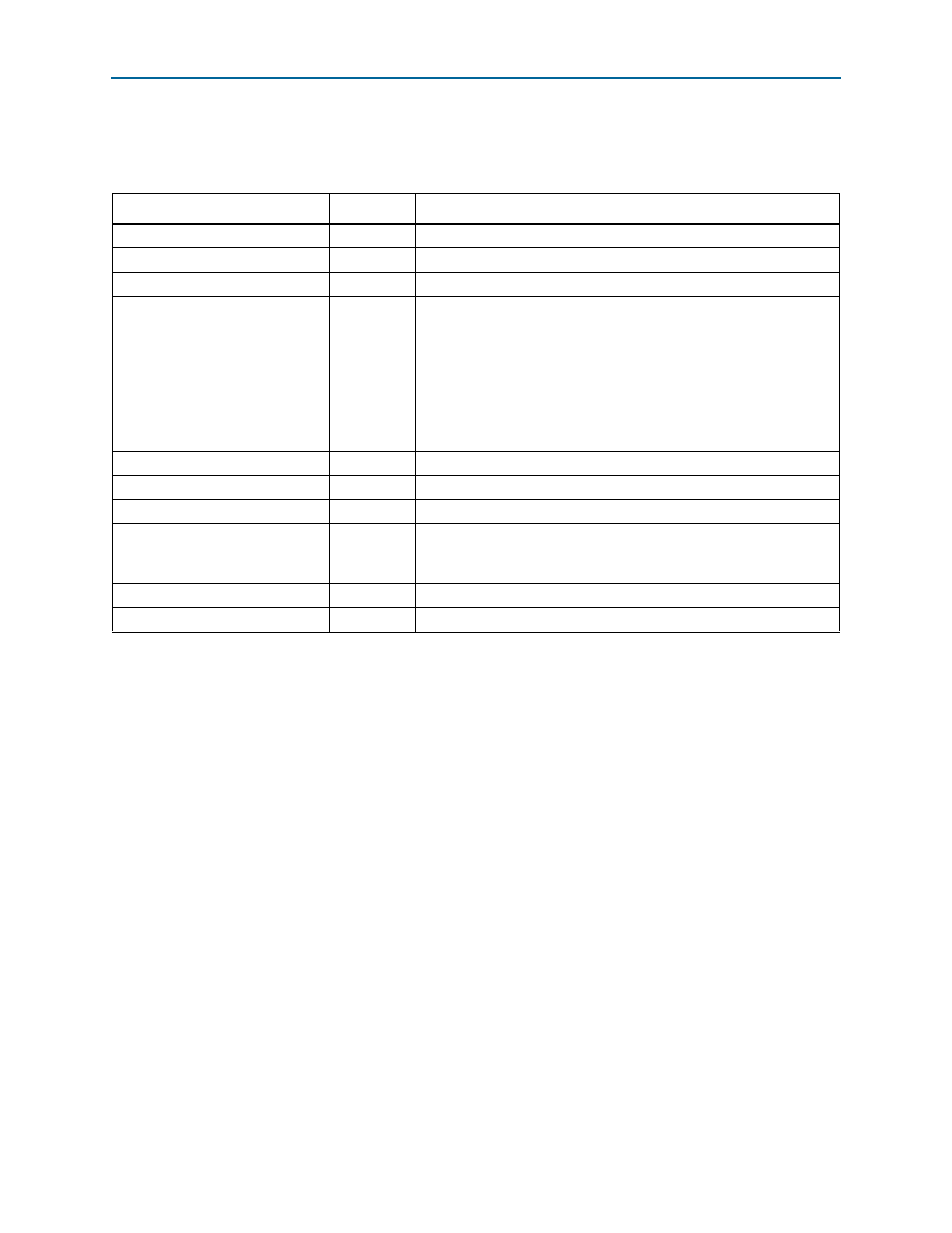

Table 4–9. Input/Output Avalon-MM Slave Interface Signals

Signal

Direction

Description

ios_rd_wr_waitrequest

Output

I/O Logical Layer Avalon-MM Slave module wait request.

ios_rd_wr_write

Input

I/O Logical Layer Avalon-MM Slave module write request.

ios_rd_wr_read

Input

I/O Logical Layer Avalon-MM Slave module read request.

ios_rd_wr_address[N:0]

for N == 9, 10,..., or 31

Input

I/O Logical Layer Avalon-MM Slave module address bus. The address

is a quad-word address (addresses a 16-byte (128-bit) quad-word),

not a byte address.

“Defining the Input/Output Avalon-MM Slave Address Mapping

for information about the RapidIO II IP core

process to determine the values for the corresponding RapidIO packet

header fields. You determine the width of the ios_rd_wr_address

bus in the RapidIO II parameter editor.

ios_rd_wr_writedata[127:0]

Input

I/O Logical Layer Avalon-MM Slave module write data bus.

ios_rd_wr_byteenable[15:0]

Input

I/O Logical Layer Avalon-MM Slave module byte enable.

ios_rd_wr_burstcount[4:0]

Input

I/O Logical Layer Avalon-MM Slave module burst count.

ios_rd_wr_readresponse

Output

I/O Logical Layer Avalon-MM Slave module read error response. I/O

Logical Layer Avalon-MM Slave module read error. Indicates that the

burst read transfer did not complete successfully.

ios_rd_wr_readdata[127:0]

Output

I/O Logical Layer Avalon-MM Slave module read data bus.

ios_rd_wr_readdatavalid

Output

I/O Logical Layer Avalon-MM Slave module read data valid.