Altera RapidIO II MegaCore Function User Manual

Page 53

Chapter 4: Functional Description

4–11

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

The I/O Avalon-MM Master module supports an interrupt line, io_m_mnt_irq, on the

Register Access interface. When enabled, the following interrupts assert the

io_m_mnt_irq

signal:

■

Address out of bounds

For more information about the I/O Logical layer Avalon-MM master module

interrupts, refer to

Defining the Input/Output Avalon-MM Master Address Mapping Windows

When you specify the value for Number of Rx address translation windows in the

RapidIO II parameter editor, you determine the number of address translation

windows available for translating incoming RapidIO read and write transactions to

Avalon-MM requests on the I/O Logical layer Master port.

You must program the Input/Output Master Mapping Window registers to support the

address ranges you wish to distinguish. You can disable an address translation

window that is available in your configuration, but the maximum number of

windows you can program is the number you specify in the RapidIO II parameter

editor with the Number of Rx address translation windows value.

The RapidIO II IP core includes one set of Input/Output Master Mapping Window

registers for each translation window. The following registers define address

translation window n:

■

A base register: Input/Output Master Mapping Window n Base (

)

■

A mask register: Input/Output Master Mapping Window n Mask (

■

An offset register: Input/Output Master Mapping Window n Offset (

You can change the values of the window defining registers at any time. You should

disable a window before changing its window defining registers.

To enable a window, set the window enable (WEN) bit of the window’s Input/Output

Master Mapping Window

n Mask register (

) to the value of 1. To

disable it, set the WEN bit to the value of zero.

For each defined and enabled window, the RapidIO II IP core masks out the RapidIO

address's least significant bits with the window mask and compares the resulting

address to the window base.

The matching window is the lowest numbered window for which the following

equation holds:

(rio_addr[33:4]

& {xamm[1:0], mask[31:4]})

==

({xamb[1:0], base[31:4]} & {xamm[1:0], mask[31:4]})

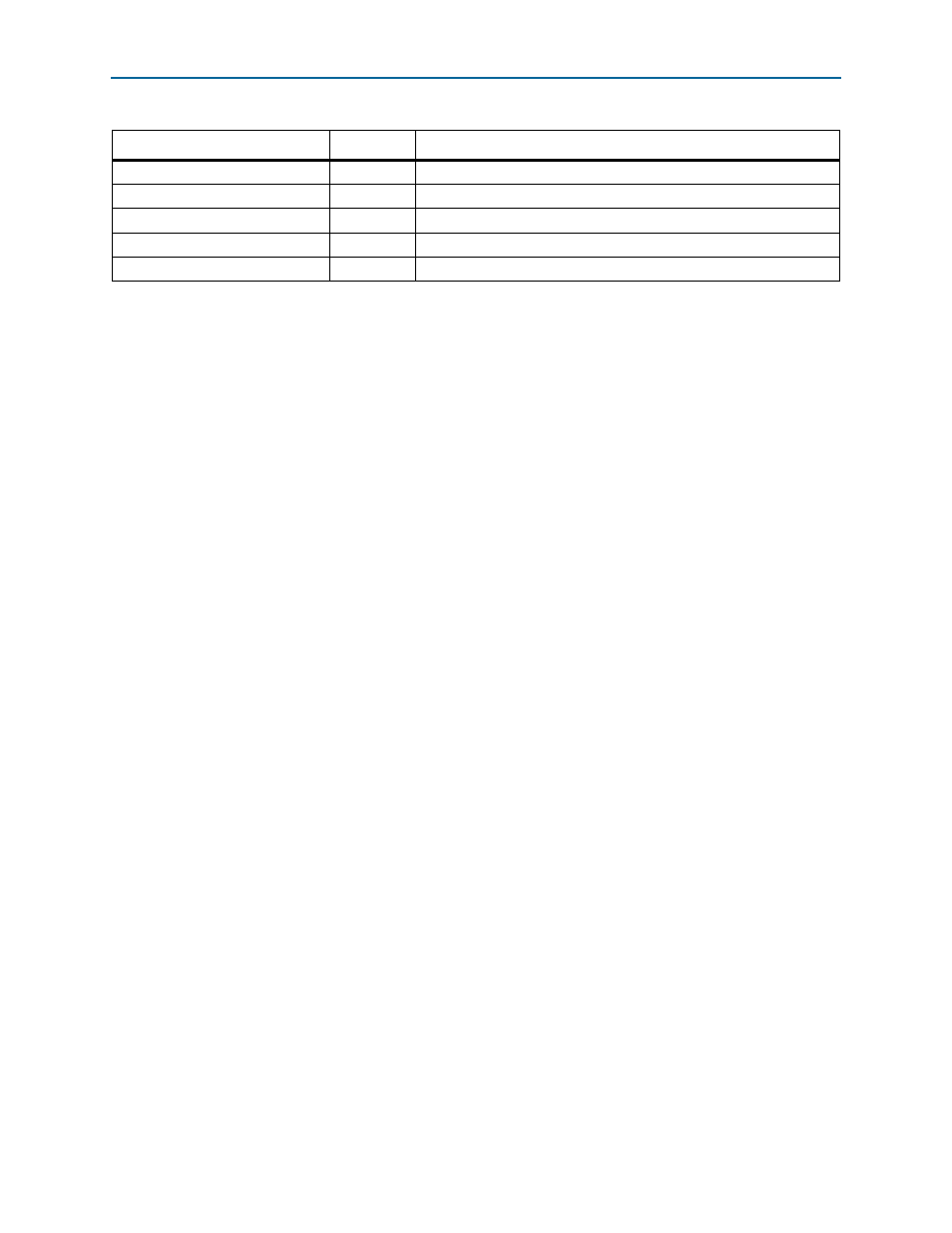

iom_rd_wr_byteenable[15:0]

Output

I/O Logical Layer Avalon-MM Master module byte enable.

iom_rd_wr_burstcount[4:0]

Output

I/O Logical Layer Avalon-MM Master module burst count.

iom_rd_wr_readresponse

Input

I/O Logical Layer Avalon-MM Master module read error response.

iom_rd_wr_readdata[127:0]

Input

I/O Logical Layer Avalon-MM Master module read data bus.

iom_rd_wr_readdatavalid

Input

I/O Logical Layer Avalon-MM Master module read data valid.

Table 4–5. Input/Output Avalon-MM Master Interface Signals (Part 2 of 2)

Signal

Direction

Description