Recovered data clock, Clock rate relationships in the rapidio ii ip core, Clock domains in your qsys system – Altera RapidIO II MegaCore Function User Manual

Page 46: Reset for rapidio ii ip cores, Reset for rapidio ii

4–4

Chapter 4: Functional Description

Clocking and Reset Structure

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

f

For more information about using high-speed transceiver blocks, refer to the relevant

device handbook.

Recovered Data Clock

The clock and data recovery block (CDR) in the transceiver recovers this clock,

rx_clkout

, from the incoming RapidIO data. The RapidIO II IP core provides this

output clock as a convenience. You can use it to source a system-wide clock with a

0 PPM frequency difference from the clock used to transmit the incoming data.

Clock Rate Relationships in the RapidIO II IP Core

The RapidIO v2.2 specification specifies baud rates of 1.25, 2.5, 3.125, 5.0, and

6.25 Gbaud.

Table 4–3

lists the clock rates in the different RapidIO II IP core variations, showing

the relationship between baud rate, default transceiver reference clock frequency, and

Avalon system clock frequency.

Clock Domains in Your Qsys System

In systems created with Qsys, the system interconnect manages clock domain crossing

if some of the components of the system run on a different clock. For optimal

throughput, run all the components in the datapath on the same clock.

Reset for RapidIO II IP Cores

All RapidIO II IP core variations have the following reset signals:

■

rst_n

—resets the RapidIO II IP core

■

tx_ready

, tx_analogreset, tx_digitalreset—reset the transmit side of the

transceiver

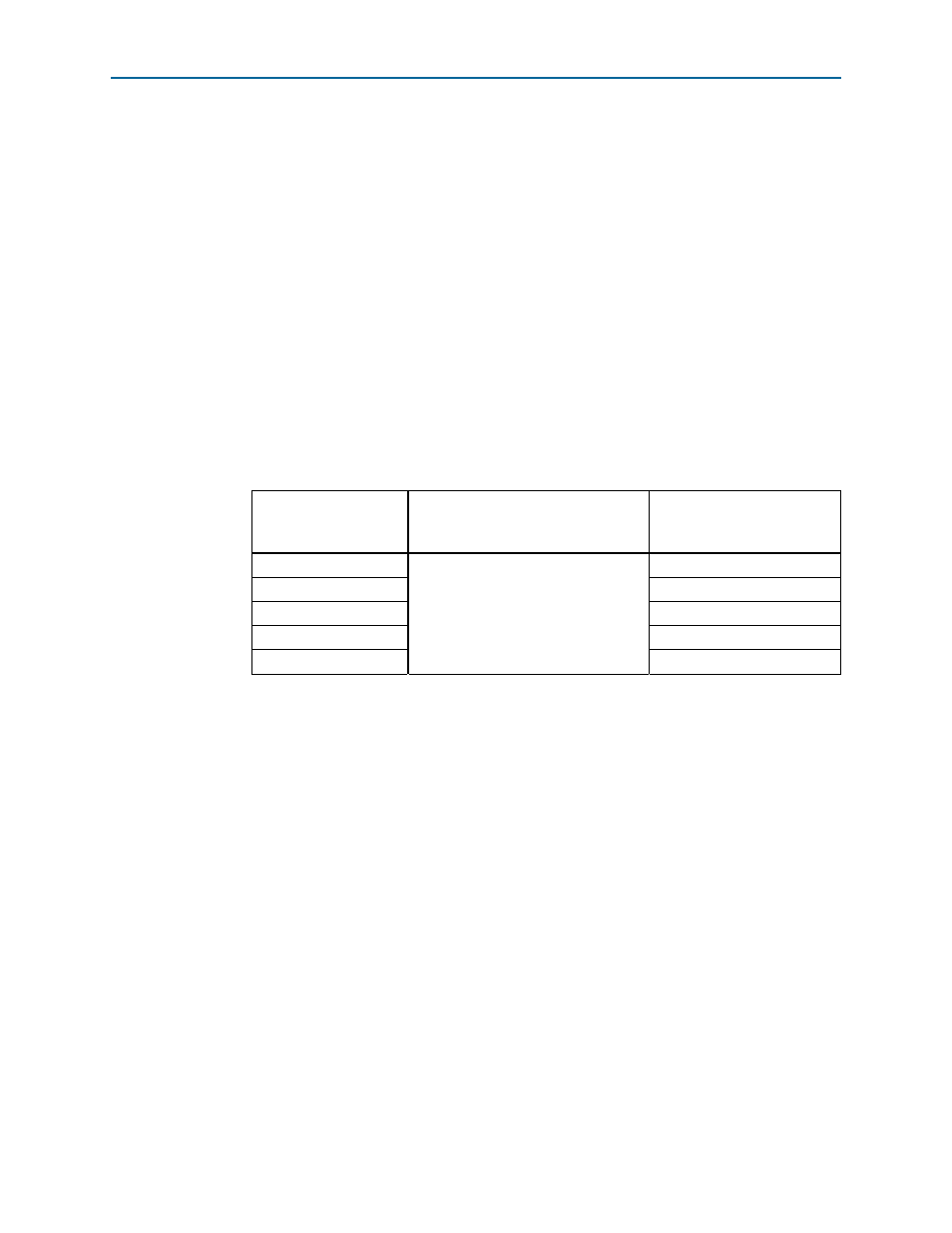

Table 4–3. Clock Frequencies in the RapidIO II IP Core

Baud Rate

(Gbaud)

Default reference clock frequency

(2)

(MHz)

Avalon system clock

Frequency

(3)

(MHz)

1.25

156.25

31.25

2.5

62.5

3.125

78.125

5.0

125.0

6.25

156.25

Notes to

Table 4–3

:

(1) For information about the allowed reference clock frequencies, refer to

(2) The reference clock is called tx_pll_refclk by default.

(3) The Avalon system clock is called sys_clk by default. It runs at 1/40 the frequency of the maximum baud rate you

configure in the RapidIO II parameter editor, irrespective of the baud rate you program in software. You must drive

sys_clk

and the reference clock from the same clock source.