Simulating the testbench with the vcs simulator, Integrating your ip core in your design, Simulating the testbench with the vcs simulator –6 – Altera RapidIO II MegaCore Function User Manual

Page 24: Integrating your ip core in your design –6

2–6

Chapter 2: Getting Started

Integrating Your IP Core in Your Design

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

Simulating the Testbench with the VCS Simulator

To simulate the RapidIO II IP core testbench using the Synopsys VCS simulator,

perform the following steps:

1. Change directory to the directory where the testbench simulation script is located:

■

For Arria 10 variations, change directory to <variation>/sim/synopsys/vcs.

■

For all other variations you generate from the Quartus II IP Catalog, change

directory to <variation>_sim/synopsys/vcs.

■

For all other variations you generate from the Qsys IP Catalog, change

directory to <Qsys system>/simulation/synopsys/vcs

2. Type the following commands:

sh vcs_setup.sh TOP_LEVEL_NAME="tb_rio"

./simv

Integrating Your IP Core in Your Design

When you integrate your IP core instance in your design, you must pay attention to

some additional requirements. If you generate your IP core from the Qsys IP catalog

and build your design in Qsys, you can perform these steps in Qsys. If you generate

your IP core directly from the Quartus II IP catalog, you must implement these steps

manually in your design.

Dynamic Transceiver Reconfiguration Controller for Arria V, Arria V GZ,

Cyclone V, and Stratix V Variations

RapidIO II IP core variations that target an Arria V, Arria V GZ, Cyclone V, or Stratix

V device require an external reconfiguration controller to function correctly in

hardware. RapidIO II IP core variations that target an Arria 10 device include a

reconfiguration controller block and do not require an external reconfiguration

controller. However, you need to control dynamic transceiver reconfiguration in Arria

10 devices through the Arria 10 dynamic reconfiguration interface if you turn on that

interface in the RapidIO II parameter editor.

Keeping the reconfiguration controller external to the IP core in these devices

provides the flexibility to share the reconfiguration controller among multiple IP cores

and to accommodate FPGA transceiver layouts based on the usage model of your

application. In Arria 10 devices, you can configure individual transceiver channels

flexibly through an Avalon-MM Arria 10 transceiver reconfiguration interface.

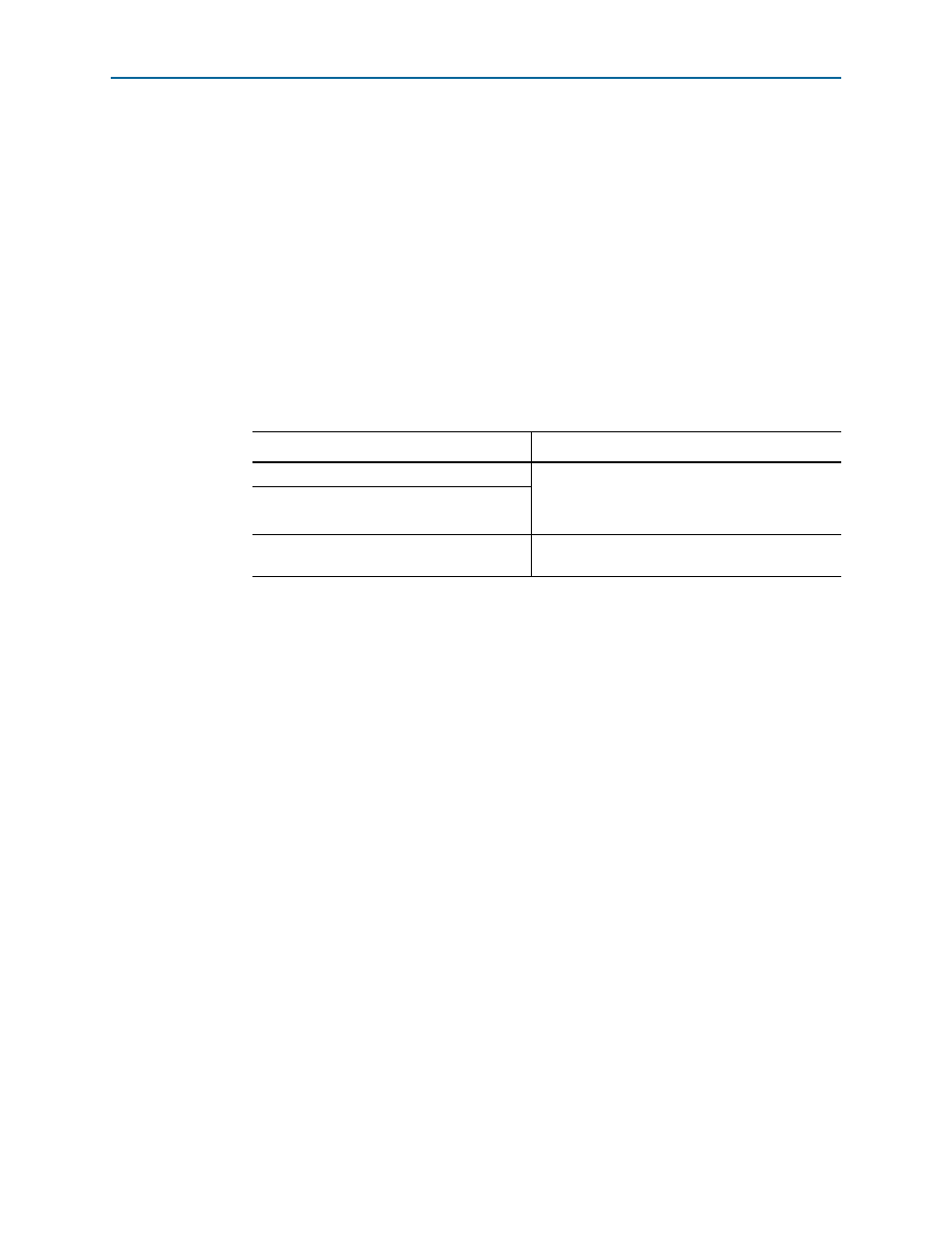

f

For Information About

Refer To

Quartus II software

See the Quartus II Help topics:

“About the Quartus II Software”

“About the IP Catalog”

IP Catalog

Altera simulation models

Simulating Altera Designs

chapter in volume 3 of

the Quartus II Handbook