Altera RapidIO II MegaCore Function User Manual

Page 165

Chapter 6: Software Interface

6–27

Transport and Logical Layer Registers

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

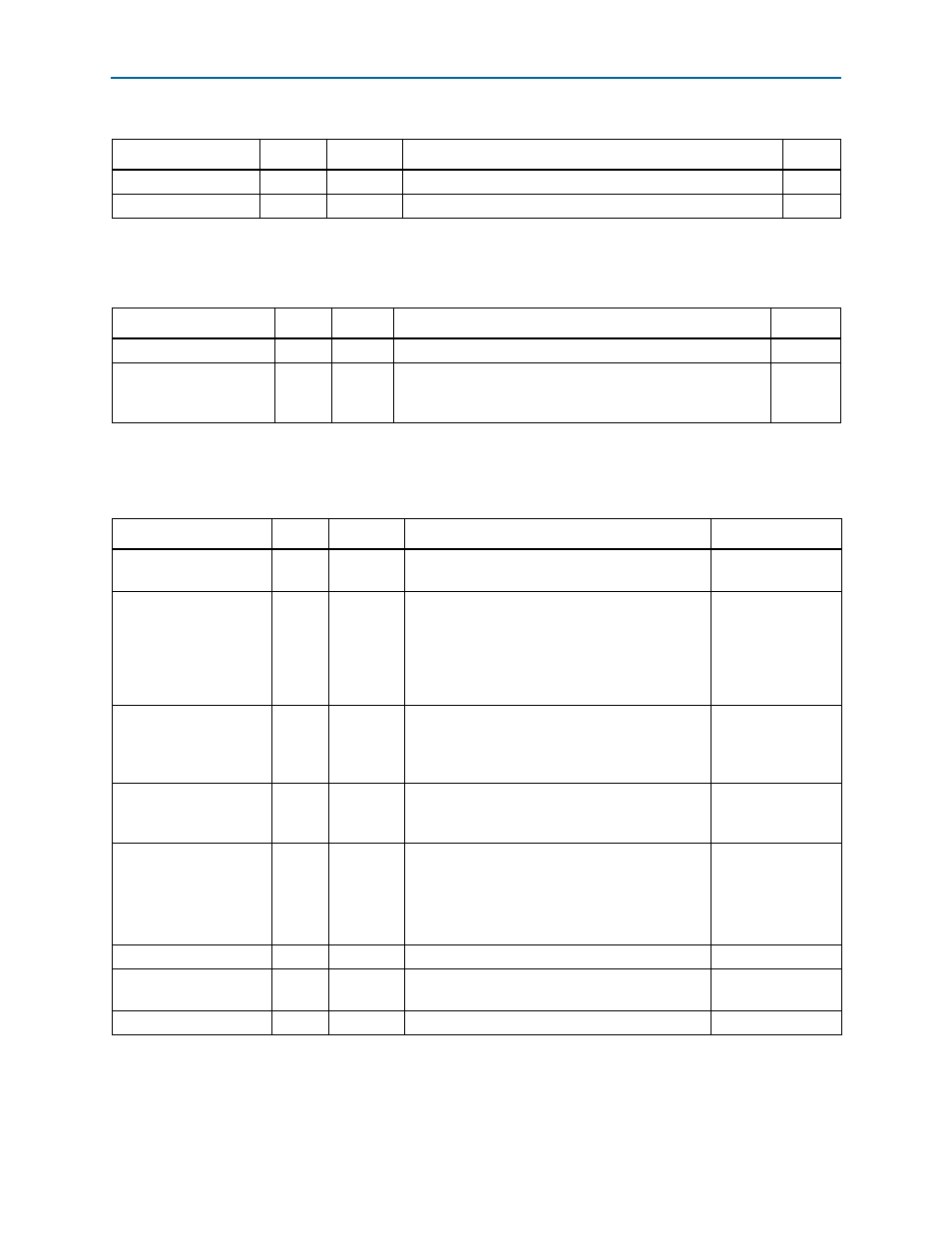

Table 6–24. Assembly Identity CAR—Offset: 0x08

Field

Bits

Access

Function

Default

AssyIdentity

[31:16]

RO

Hard-wired assembly identifier

AssyVendorIdentity

[15:0]

RO

Hard-wired assembly vendor identifier

Note to

:

(1) The value is set in the RapidIO II parameter editor.

Table 6–25. Assembly Information CAR—Offset: 0x0C

Field

Bits

Access

Function

Default

AssyRev

[31:16] RO

Hard-wired assembly revision level

ExtendedFeaturesPtr

[15:0]

RO

Hard-wired pointer to the first entry in the extended feature.

The value of this field is 0x100, which points to the LP-Serial

Extended Features block.

16’h100

Note to

:

(1) The value is set in the RapidIO II parameter editor.

Table 6–26. Processing Element Features CAR—Offset: 0x10 (Part 1 of 2)

Field

Bits

Access

Function

Default

Bridge

[31]

RO

Processing element can bridge to another

interface.

Memory

[30]

RO

Processing element has physically addressable

local address space and can be accessed as an

endpoint through non-maintenance operations.

This local address space may be limited to local

configuration registers, on-chip SRAM, or other

device.

Processor

[29]

RO

Processing element physically contains a local

processor or similar device that executes code. A

device that bridges to an interface that connects to

a processor does not count.

Switch

[28]

RO

Processing element can bridge to another external

RapidIO interface—an internal port to a local

endpoint does not count as a switch port.

MULTIPORT

[27]

RO

Processing element implements multiple external

RapidIO ports.

The RapidIO II IP core implements only a single

RapidIO port, so this field always has the value of

1’b0.

1'h0

RSRV

[26:12] RO

Reserved

25'h0

Flow Arbitration

Support

[11]

RO

Processing element supports flow arbitration.

RSRV

[10]

RO

Reserved

1'h0