Table 4–26 – Altera RapidIO II MegaCore Function User Manual

Page 93

Chapter 4: Functional Description

4–51

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

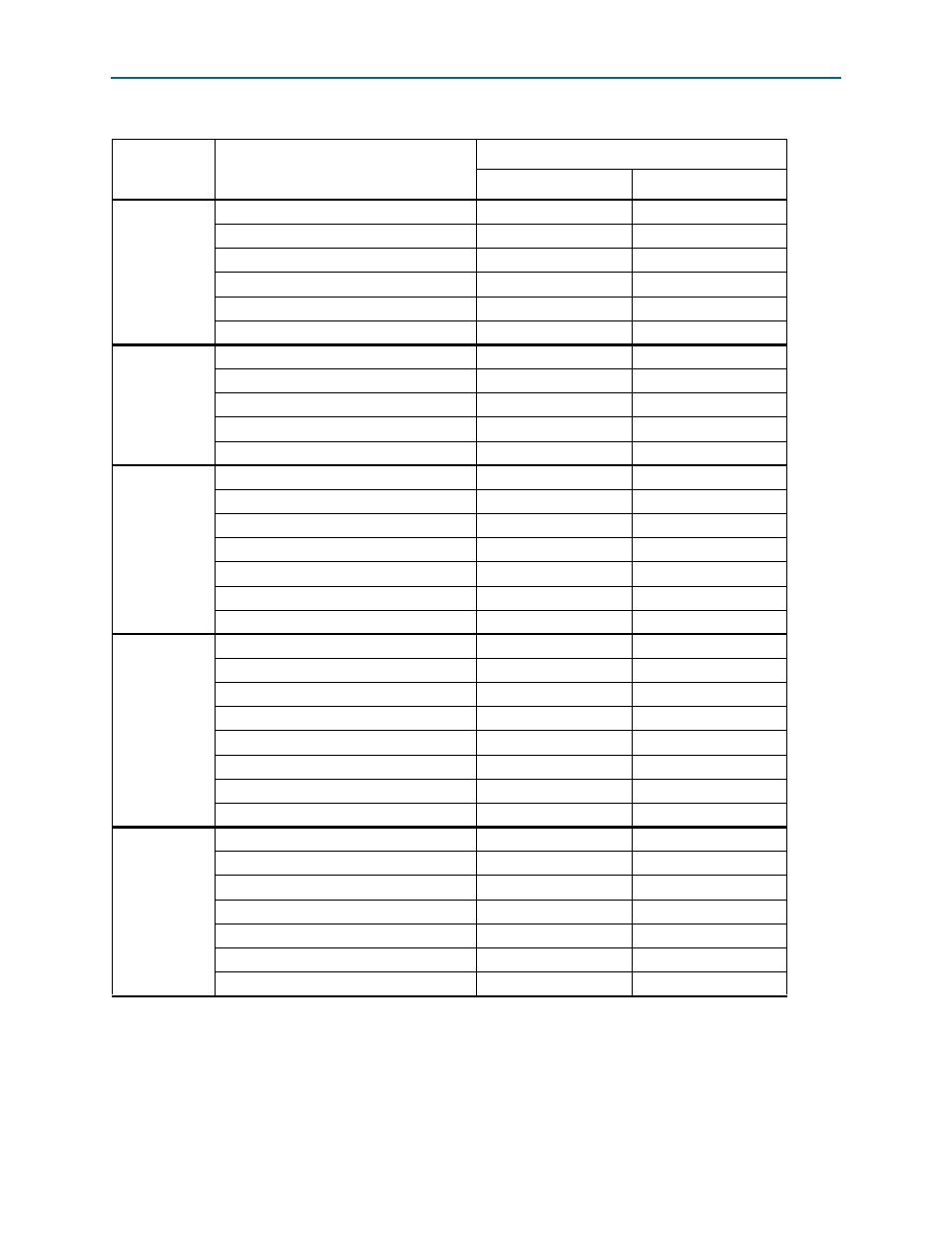

Table 4–26. specific_header Format on gen_tx_data Bus (Part 1 of 2)

ftype

Field

gen_tx_data Bits

Device ID Width 8

Device ID Width 16

2, 5, or 6

ttype[3:0]

[95:92]

[79:76]

size[3:0]

[91:88]

[75:72]

transactionID[7:0]

[87:80]

[71:64]

address[28:0]

[79:51]

[63:35]

wdptr

[50]

[34]

xamsbs[1:0]

[49:48]

[33:32]

7

XON/XOFF

[95]

[79]

FAM[2:0]

[94:92]

[78:76]

Reserved[3:0]

[91:88]

[75:72]

flowID[6:0]

[87:81]

[71:65]

soc

[80]

[64]

8

ttype[3:0]

[95:92]

[79:76]

size[3:0]

[91:88]

[75:72]

transactionID[7:0]

[87:80]

[71:64]

hop_count[7:0]

[79:72]

[63:56]

config_offset[20:0]

[71:51]

[55:35]

wdptr

[50]

[34]

Reserved[1:0]

[49:48]

[33:32]

9 single

segment and

start

cos[7:0]

[95:88]

[79:72]

S

[87]

[71]

E

[86]

[70]

Reserved[2:0]

[85:83]

[69:67]

xh

[82]

[66]

O

[81]

[65]

P

[80]

[64]

streamID[15:0]

[79:64]

[63:48]

9 continuation

cos[7:0]

[95:88]

[79:72]

S

[87]

[71]

E

[86]

[70]

Reserved[2:0]

[85:83]

[69:67]

xh

[82]

[66]

O

[81]

[65]

P

[80]

[64]