Altera RapidIO II MegaCore Function User Manual

Page 211

Appendix B: Differences Between RapidIO II MegaCore Function v12.1 and RapidIO MegaCore Function v12.1

B–3

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

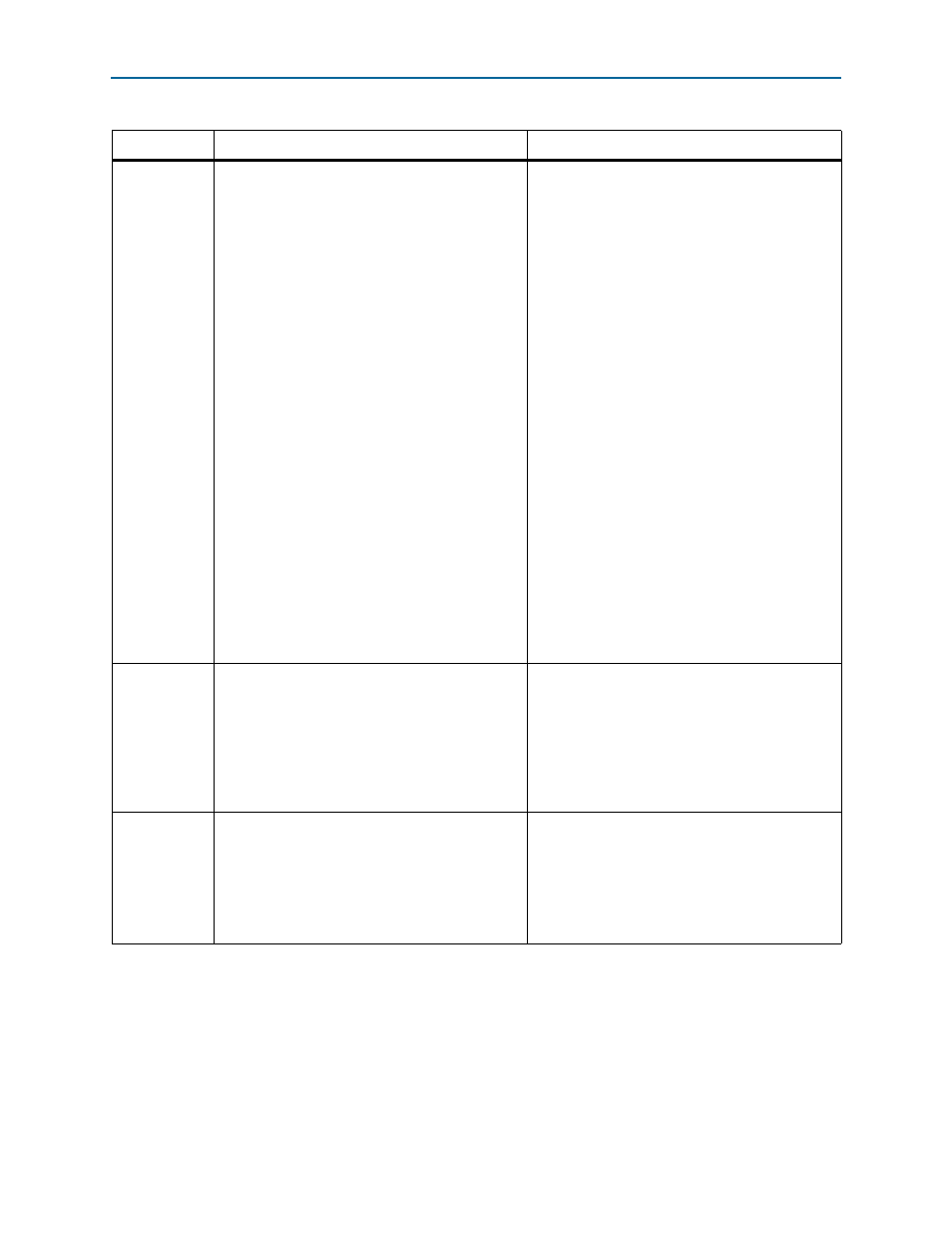

Registers

■

Fully complies with Part 8: Error Management

Extensions Specification of the RapidIO

Interconnect Specification, Revision 2.2

■

Supports the LP-Serial Lane Extended Features

registers described in RapidIO Interconnect

Specification v2.2 Part 6: LP-Serial Physical

Layer Specification for up to four lanes, with two

implementation-specific registers per lane.

■

Various register field differences with RapidIO IP

core.

■

For example, the NWRITE_RS_COMPLETED

field in the I/O Slave Interrupt and I/O

Slave Interrupt Enable

registers is not

available in the RapidIO II IP core. However,

these two registers support

INVALID_READ_BYTEENABLE

and

INVALID_READ_BURSTCOUNT

interrupts.

■

For example, the information found in the

PROMISCUOUS_MODE

field of the Rx

Transport Control

register in the

RapidIO IP core is found in the

DIS_DEST_ID_CHK

field of the Port 0

Control CSR

in the RapidIO II IP core, which

has no Rx Transport Control register.

For details of the registers in the RapidIO II IP core,

refer to

The RapidIO IP core implements a subset of the

optional Error Management Extensions as defined in

Part 8 of the RapidIO Interconnect Specification

Revision 2.1. However, because the registers

defined in the Error Management Extension

specification are not all implemented in the RapidIO

IP core, the error management registers are

mapped in the Implementation Defined Space

instead of being mapped in the Extended Features

Space.

The RapidIO IP core does not implement the

LP-Serial Lane Extended Features registers.

Interrupt

signals

The RapidIO II IP core generates interrupts on

multiple module- and block-specific output signals.

The specific triggering conditions are noted in

registers, as in the RapidIO IP core. The RapidIO II

IP core generates all Doorbell module specific

interrupt conditions with the drbell_s_irq signal.

The RapidIO IP core generates interrupts on two

output signals, the sys_mnt_s_irq signal and the

drbell_s_irq

signal. The sys_mnt_s_irq signal

indicates all interrupt conditions that the RapidIO IP

core indicates in registers, except the Doorbell

module specific interrupt conditions. The RapidIO

IP core generates all Doorbell module specific

interrupt conditions with the drbell_s_irq signal.

byteenable

value for read

requests on

the I/O Logical

layer Master

and Slave

interfaces

Read transactions on the I/O Logical layer Master

and Slave interfaces have associated byteenable

values.

Read transactions on the I/O Logical layer Master

and Slave interfaces have no associated byteenable

value. The byteenable value is assumed to be all

ones. User logic is responsible for enforcing any

required byte masking in the read data it receives,

and is required to return full 32- or 64-bit words of

read data.

Table B–1. Major Differences Between the RapidIO II IP Core v12.1 and the RapidIO IP Core v12.1 (Part 3 of 4)

Property

RapidIO II IP Core v12.1

RapidIO IP Core v12.1