Altera RapidIO II MegaCore Function User Manual

Page 81

Chapter 4: Functional Description

4–39

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

write transaction. In the example, the IP core throttles the incoming transaction for

five clock cycles, because it requires six clock cycles to process each write transaction.

The user logic maintains the values on the mnt_s_write, mnt_s_writedata, and

mnt_s_address

signals until one clock cycle after the IP core deasserts the

mnt_s_waitrequest

signal, as required by the Avalon-MM specification. In the

following clock cycle, user logic sends the next write request, which the IP core also

throttles for five clock cycles. The process repeats for an additional two write requests.

The RapidIO II IP core converts these write transactions to RapidIO MAINTENANCE

request packets.

Table 4–17

lists the fields in the corresponding RapidIO packets.

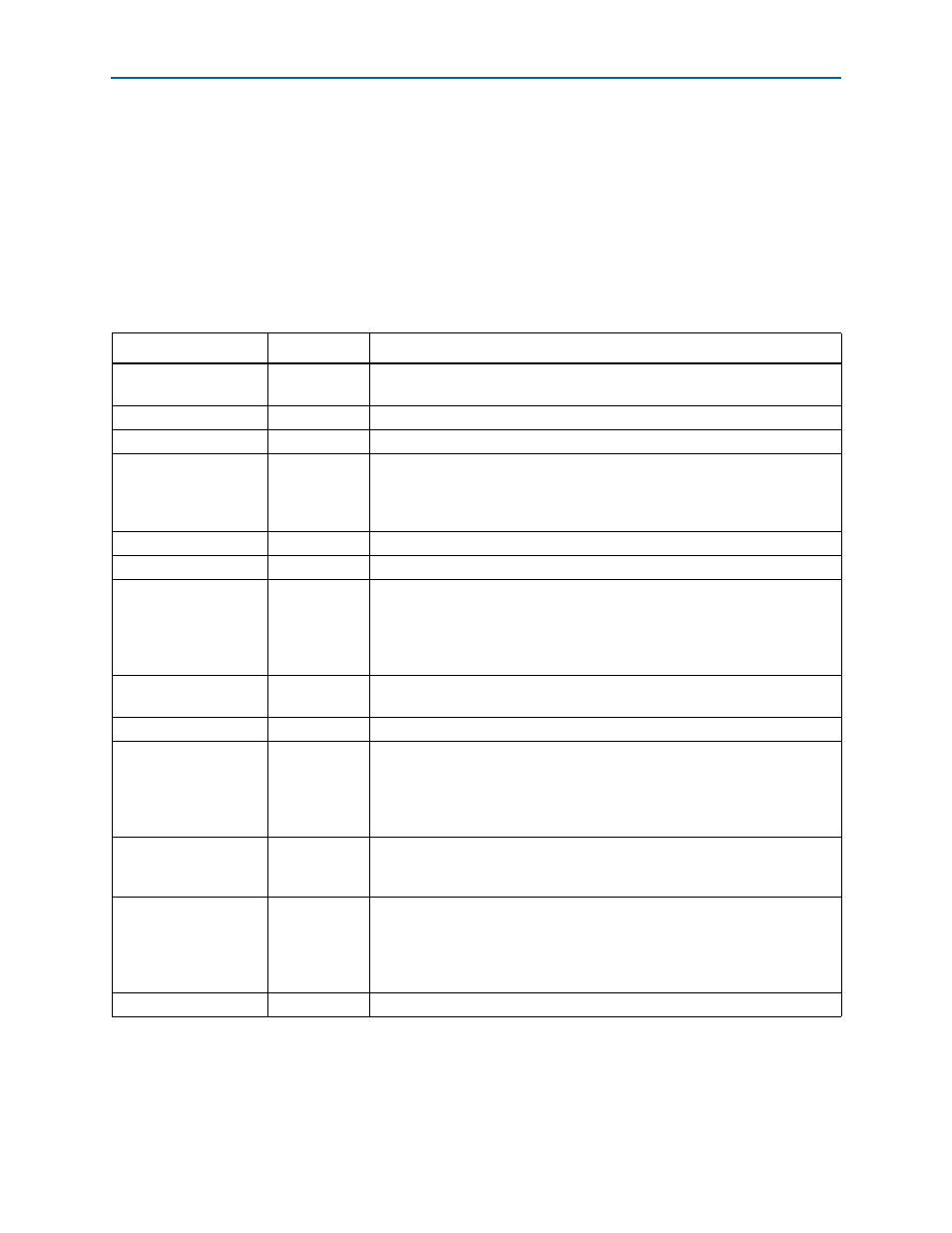

Table 4–17. Maintenance Write Request Transmit Example: RapidIO Packet Fields (Part 1 of 2)

Field

Value

Comment

ackID

6'h00

Value is written by the Physical layer before the packet is transmitted on the

RapidIO link.

VC

0

The RapidIO II IP core supports only VC0.

CRF

0

prio[1:0]

2'b00

The IP core assigns to this field the value programmed in the PRIORITY field of

the Tx Maintenance Mapping Window n Control register (

) for the matching address translation window n. Refer to

“Defining

the Maintenance Address Translation Windows” on page 4–34

for details.

tt[1:0]

2'b00

The value of 0 indicates 8-bit device IDs.

ftype[3:0]

4'b1000

The value of 8 indicates a Maintenance Class packet.

destinationID[7:0]

The IP core assigns to this field the value programmed in the DESTINATION_ID

field of the Tx Maintenance Mapping Window n Control register

(

) for the matching address translation window n.

Refer to

“Defining the Maintenance Address Translation Windows” on

page 4–34

for matching details.

sourceID[7:0]

The IP core assigns to this field the value programmed in the Base_deviceID

field of the Base Device ID register (offset 0x60).

ttype[3:0]

4’b0001

The value of 1 indicates a MAINTENANCE write request.

wrsize[3:0]

4'b1000

The size and wdptr values encode the maximum size of the payload field. In

MAINTENANCE

transactions, the value of wrsize is always 4’b1000, which

decodes to a value of 4 bytes. For encoding details, refer to Table 4-4 in Part 1:

Input/Output Logical Specification of the RapidIO Interconnect Specification,

Revision 2.2.

srcTID[7:0]

The RapidIO II IP core generates the source transaction ID value internally to

track the transaction response. The value depends on the current state of the

RapidIO II IP core when it prepares the RapidIO packet.

config_offset[20:0]

Depends on the value on the mnt_s_address bus, and the values programmed

in the Tx Maintenance Address Translation Window registers, as

defined in

. Refer to

“Defining the Maintenance

Address Translation Windows” on page 4–34

for the matching and conversion

calculations.

wdptr

The IP core assigns to this field the negation of mnt_s_address[0].