Pass-through interface signals, Pass-through interface signals –49 – Altera RapidIO II MegaCore Function User Manual

Page 91

Chapter 4: Functional Description

4–49

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

If the Input-Output Avalon-MM slave module or the Doorbell Logical layer module is

not instantiated, the RapidIO II IP core Transport layer routes the response packets in

the corresponding Transaction IDs ranges for these layers to the Avalon-ST

pass-through interface.

Pass-Through Interface Signals

The Avalon-ST pass-through interface includes the following ports:

■

Transmit interface—this sink interface accepts incoming streaming data that the IP

core sends to the RapidIO link.

■

Receive data interface—this source interface streams out the payload of packets

the IP core receives from the RapidIO link.

■

Receive header interface—this source interface streams out packet header

information the IP core receives from the RapidIO link.

Pass-Through Transmit Side Signals

lists the Avalon-ST pass-through interface transmit side signals. These

signals receive incoming streaming data from user logic; the IP core transmits this

data on the RapidIO link. The RapidIO II IP core samples data on this interface only

when both gen_tx_ready and gen_tx_valid are asserted.

The incoming streaming data is assumed to contain well-formed RapidIO packets,

with the following exceptions:

■

The streaming data includes placeholder bits for the ackID field of the RapidIO

packet, but does not include the ackID value, which is assigned by the IP core.

■

The streaming data does not include the RapidIO packet CRC bits and padding

bytes.

The Avalon-ST pass-through interface does not check the integrity of the streaming

data, but rather passes the bits on directly to the Transport layer. The RapidIO II IP

core fills in the ackID bits and adds the CRC bits and padding bytes before

transmitting each packet on the RapidIO link.

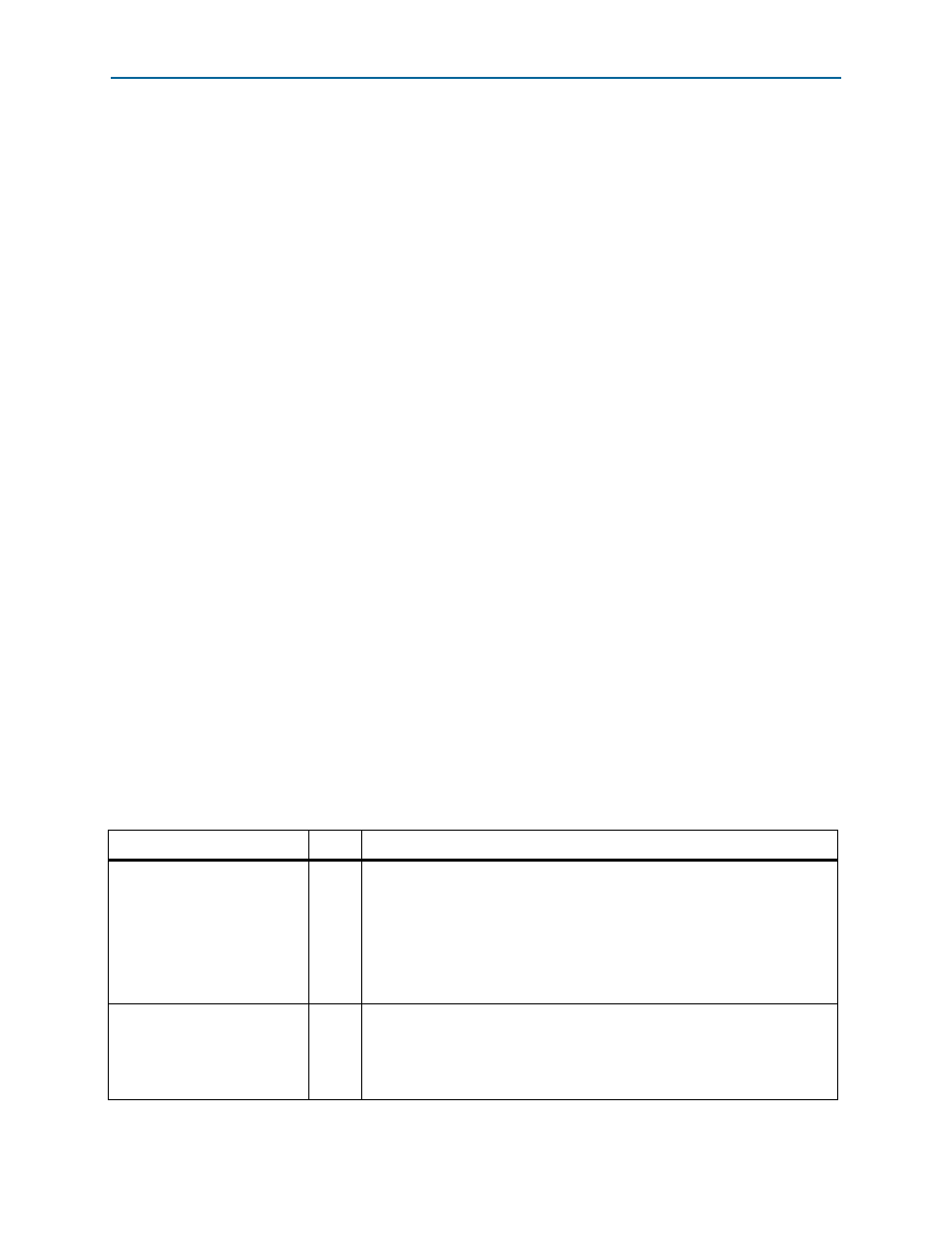

Table 4–24. Avalon-ST Pass-Through Interface Transmit Side (Avalon-ST Sink) Signals (Part 1 of 2)

Signal Name

Type

Function

gen_tx_ready

Output

Indicates that the IP core is ready to receive data on the current clock cycle.

Asserted by the Avalon-ST sink to mark ready cycles, which are the cycles in

which transfers can take place. If ready is asserted on cycle N, the cycle

(N+READY_LATENCY) is a ready cycle.

In the RapidIO II IP core, READY_LATENCY is equal to 0.

This signal may alternate between 0 and 1 when the Avalon-ST pass-through

transmitter interface is idle.

gen_tx_valid

Input

Used to qualify all the other transmit side input signals of the Avalon-ST

pass-through interface. On every ready cycle in which gen_tx_valid is high,

data is sampled by the IP core. You must assert gen_tx_valid continuously

during transmission of a packet, from the assertion of

gen_tx_startofpacket

to the deassertion of gen_tx_endofpacket.

(1)