Nread response transaction – Altera RapidIO II MegaCore Function User Manual

Page 107

Chapter 4: Functional Description

4–65

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

NREAD Response Transaction

In the first clock cycle of the NREAD response on the Avalon-ST pass-through

interface, as shown in

, the IP core asserts gen_tx_ready to indicate it is

ready to sample data. In the same cycle, user logic asserts gen_tx_valid. Because both

gen_tx_ready

and gen_tx_valid are asserted, this clock cycle is an Avalon-ST ready

cycle. The user logic provides valid data on gen_tx_data for the IP core to sample, and

asserts gen_tx_startofpacket to indicate the current value of gen_tx_data is the

initial piece of the current packet (the start of packet). On gen_tx_packet_size, user

logic reports the full length of the packet is 0x28, which is decimal 40, because the

packet comprises eight bytes of header and 32 bytes of payload data.

The user logic provides the 32-byte payload and 8-byte header on the same bus,

gen_tx_data[127:0]

. Transferring these 40 bytes of information requires three clock

cycles. During all of these cycles, the IP core holds gen_tx_ready high and user logic

holds gen_tx_valid high, indicating the cycles are all Avalon-ST ready cycles. In the

second cycle, user logic holds gen_tx_startofpacket and gen_tx_endofpacket low,

because the information on gen_tx_data is neither start of packet nor end of packet

data. In the third clock cycle, user logic asserts gen_tx_endofpacket and sets

gen_tx_empty

to the value of 0x8 to indicate that eight bytes of the data in the current

clock cycle are invalid—in other words, only the initial eight (sixteen minus eight)

bytes of data available on gen_tx_data in the current clock cycle are valid.

prio[1:0]

[103:102]

2’b01

tt[1:0]

[101:100]

2’b01

Indicates 16-bit device IDs.

ftype[3:0]

[99:96]

4'b0010

The value of 2 indicates a Request Class packet.

destinationID[15:0]

[95:80]

16’hDDDD

sourceID[15:0]

[79:64]

16’hAAAA

ttype[3:0]

[63:60]

4’b0100

The value of 4 indicates an NREAD transaction.

size[3:0]

[59:56]

4'b1100

The size and wdptr values encode the maximum size

of the payload field. In this example, they decode to a

value of 32 bytes. For details, refer to Table 4-3 in Part

1: Input/Output Logical Specification of the RapidIO

Interconnect Specification, Revision 2.2.

transactionID[7:0]

[55:48]

8'hBB

address[28:0]

[47:19]

{28’h7654321,

1’b0}

wdptr

[18]

0

Refer to the comment for size.

xamsbs[1:0]

[17:16]

2’b00

Reserved[15:0]

[15:0]

16’h0000

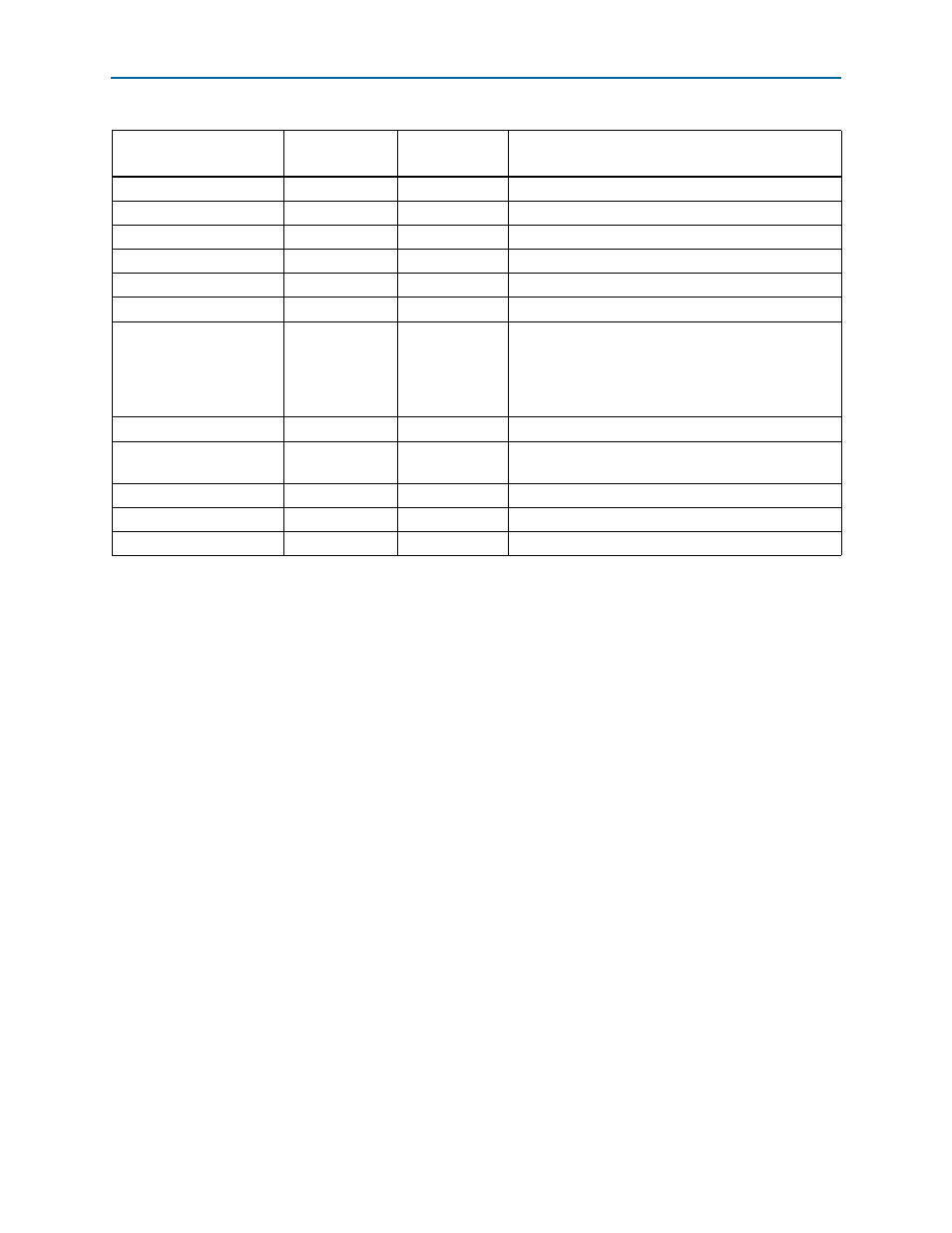

Table 4–40. NREAD Request Receive Example: RapidIO Header Fields in gen_rx_hd_data Bus (Part 2 of 2)

Field

gen_rx_hd_data

Bits

Value

Comment