Altera RapidIO II MegaCore Function User Manual

Page 145

Chapter 6: Software Interface

6–7

Physical Layer Registers

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

■

The LP-Serial Lane Extended Features block for up to four lanes, including three

implementation-specific registers per lane.

The LP-Serial Lane Extended Features block implementation-specific registers

support software-driven control of transmitter pre-emphasis for both the local and

remote ends of the RapidIO link.

Table 6–5

shows the memory map for the RapidIO II IP core Physical layer.

through

describe the registers for the Physical layer of the

RapidIO II IP core. The offset values within each of the two Extended Feature spaces

LP-Serial and LP-Serial Lane are defined by the RapidIO standard.

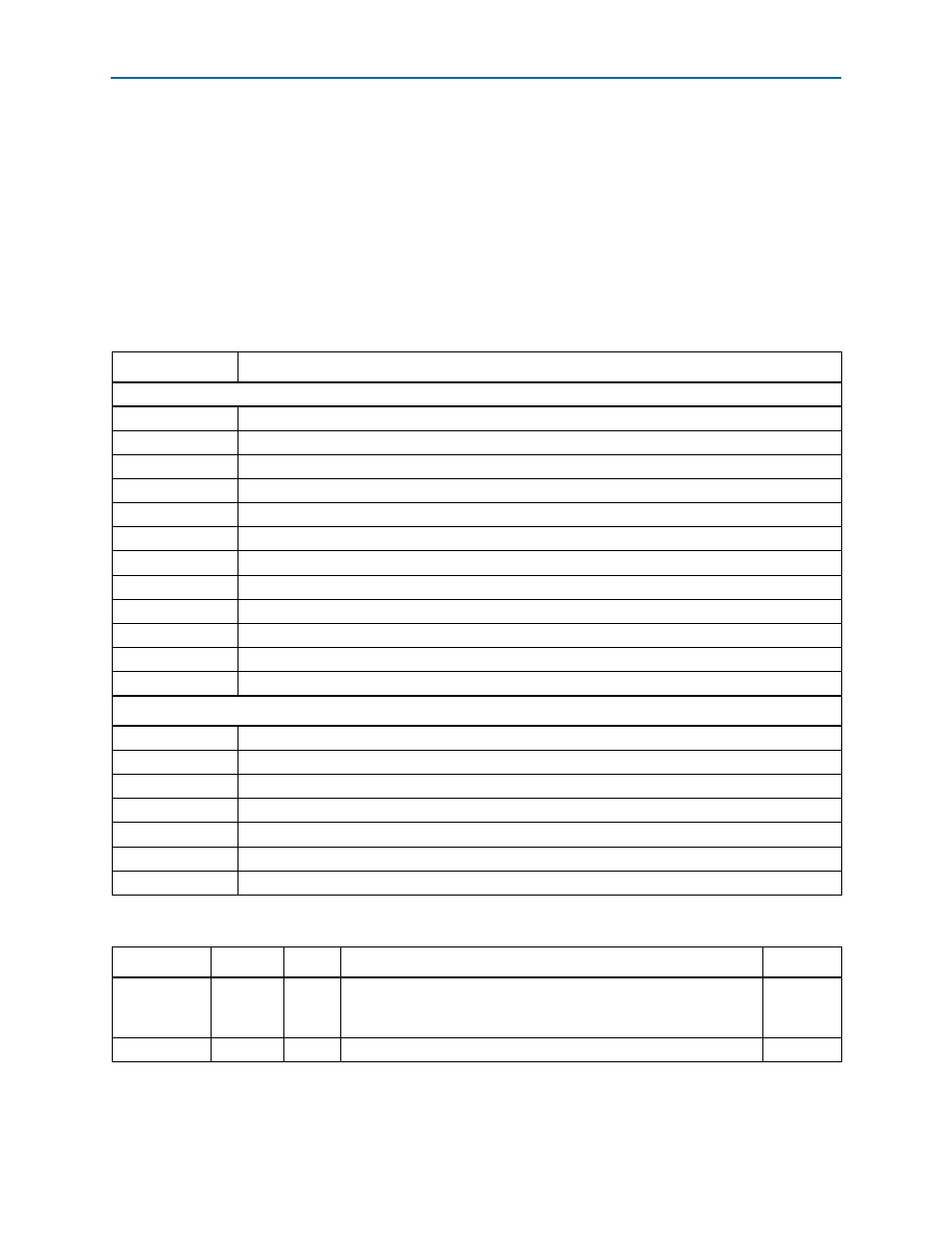

Table 6–5. Physical Layer Register Map

Address

Name

Extended Features Space: LP-Serial

0x100

LP-Serial Register Block Header

0x104–0x11C

Reserved

0x120

Port Link Time-out Control CSR

0x124

Port Response Time-out Control CSR

0x13C

Port General Control CSR

0x140

Port 0 Link Maintenance Request CSR

0x144

Port 0 Link Maintenance Response CSR

0x148

Port 0 Local AckID CSR

0x14C–0x50

Reserved

0x154

Port 0 Control 2 CSR

0x158

Port 0 Error and Status CSR

0x15C

Port 0 Control CSR

Extended Features Space: LP-Serial Lane

0x200

LP-Serial Lane Register Block Header

0x210

Lane 0 Status 0 (Local)

0x214

Lane 0 Status 1 (Far-End)

0x218

Lane 0 Status 2 (Interrupt Enable)

0x21C

Lane 0 Status 3 (Received CS Field Commands)

0x220

Lane 0 Status 4 (Outgoing CS Field)

0x230–0x280

Lane 1–3 Status

Table 6–6. LP-Serial Register Block Header—0x100

Field Bits

Access

Function

Default

EF_PTR

[31:16] RO

Hard-wired pointer to the next block in the data structure. The value in

this field is the address of the LP-Serial Lane Extended Features block,

which is 0x200.

16'h0200

EF_ID

[15:0]

RO

Hard-wired extended features ID.

16'h0002