Video mixing ip cores, Video mixing ip cores -1 – Altera Video and Image Processing Suite User Manual

Page 112

Video Mixing IP Cores

6

2015.05.04

UG-VIPSUITE

The Video Mixing IP cores mix together multiple image layers .

This run-time control is partly provided by an Avalon-MM slave port with registers for the location, and

on or off status of each foreground layer. The dimensions of each layer are then specified by Avalon-ST

Video control packets.

Note: It is expected that each foreground layer fits in the boundaries of the background layer.

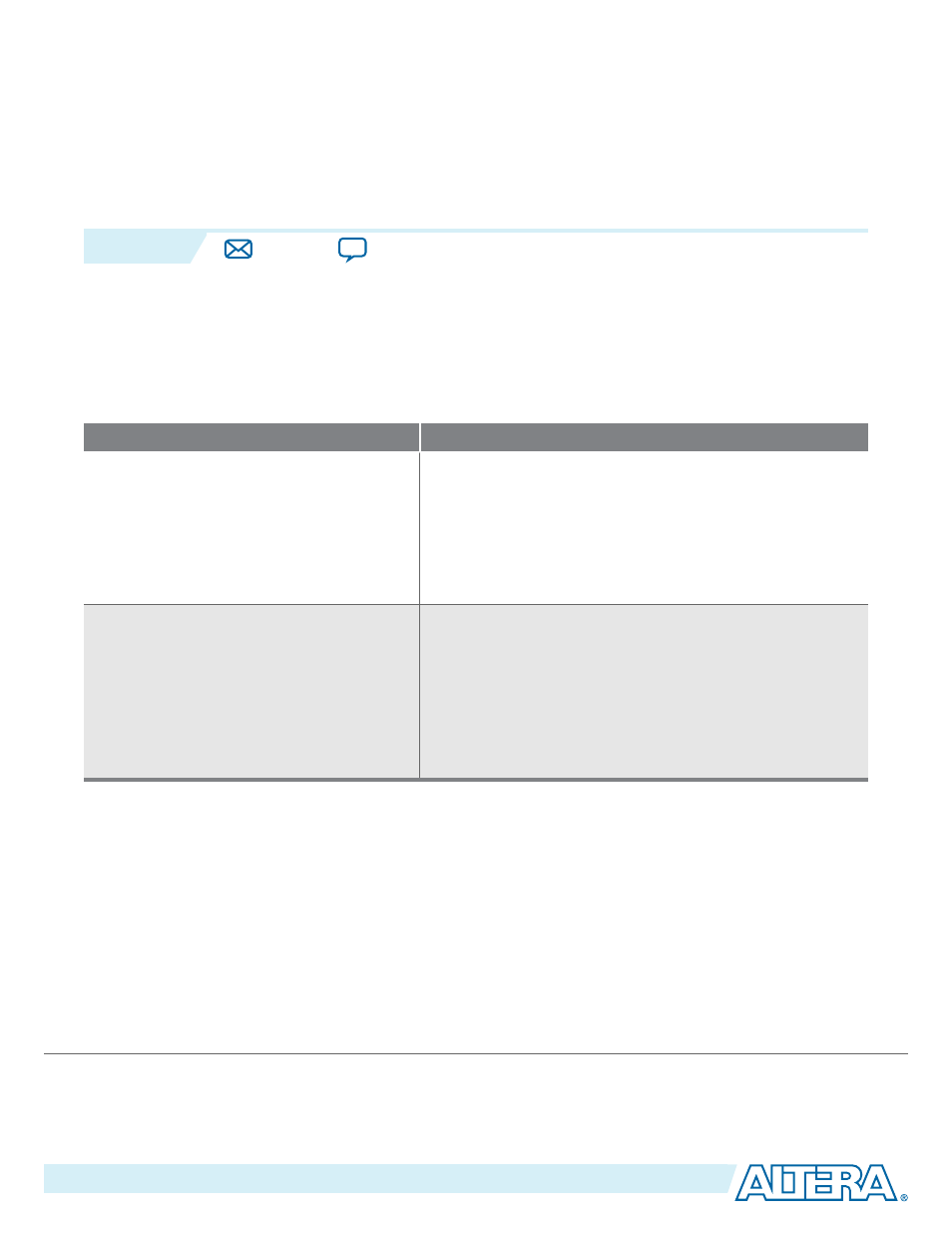

IP Cores

Feature

Alpha Blending Mixer

• Supports picture-in-picture and image blending with per

pixel alpha support.

• Supports dynamic changing of location and size of each

layer during run time.

• Allows the individual layers to be switched on and off.

• Supports 1 pixel per transmission.

Mixer II

• Supports picture-in-picture mixing.

• Supports dynamic changing of location and size of each

layer during run time.

• Allows the individual layers to be switched on and off.

• Supports up to 4 pixels in parallel.

• Includes built in test pattern generator as background

layer

The Video Mixing IP cores read the control data in two steps at the start of each frame. The buffering

happens inside the IP core so that the control data can be updated during the frame processing without

unexpected side effects.

The first step occurs after the IP core processes and transmits all the non-image data packets of the

background layer, and it has received the header of an image data packet of type 0 for the background. At

this stage, the on/off status of each layer is read. A layer can be disabled (0), active and displayed (1) or

consumed but not displayed (2). The maximum number of image layers mixed cannot be changed

dynamically and must be set in the parameter editor.

The IP core processes the non-image data packets of each active foreground layer, displayed or consumed,

in a sequential order, layer 1 first. The IP core integrally transmits the non-image data packets from the

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134