Altera Video and Image Processing Suite User Manual

Page 234

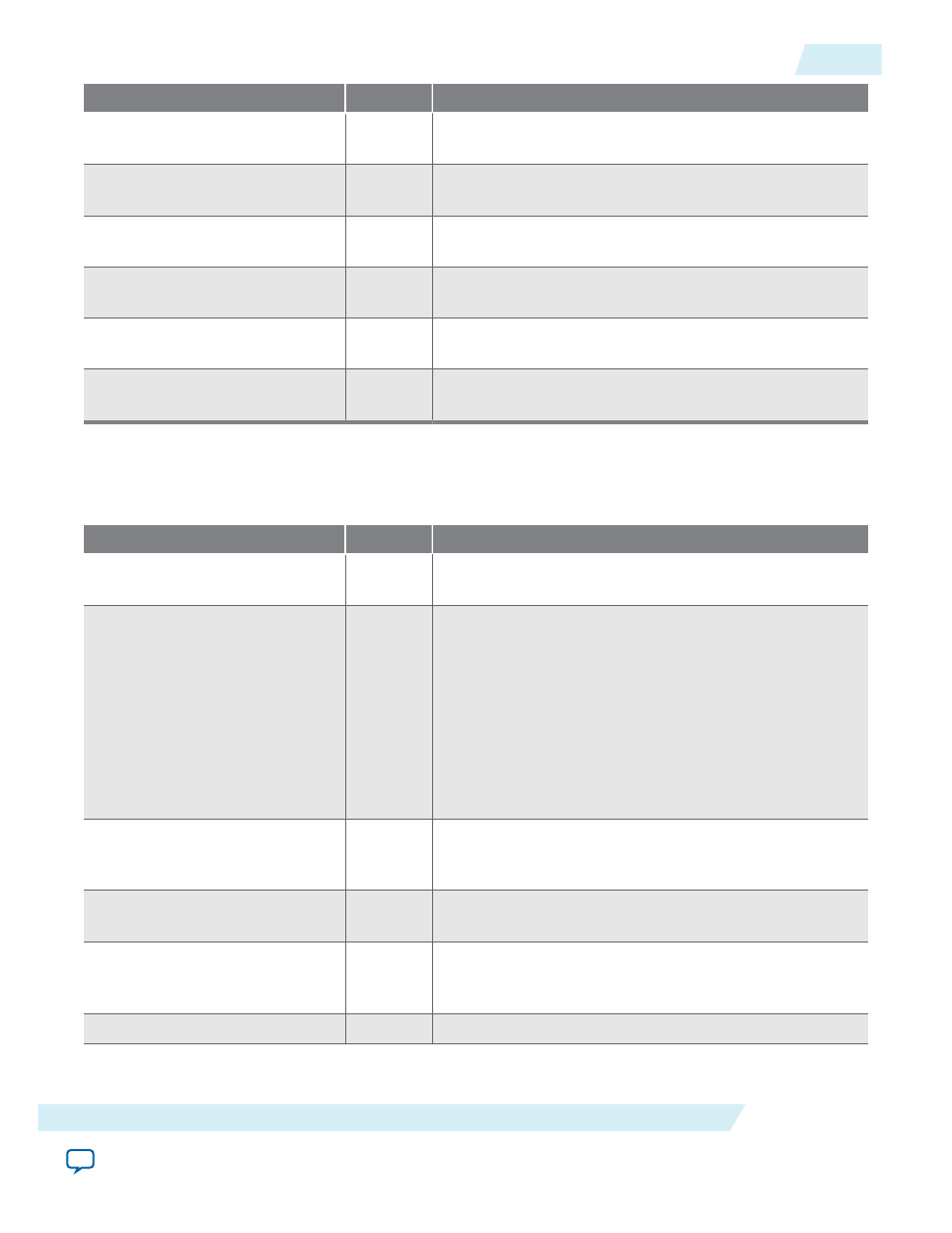

Signal

Direction

Description

din_valid

Input

din

port Avalon-ST

valid

signal. This signal identifies the

cycles when the port must enter data.

dout_data

Output

dout

port Avalon-ST

data

bus. This bus enables the

transfer of pixel data out of the IP core.

dout_endofpacket

Output

dout

port Avalon-ST

endofpacket

signal. This signal

marks the end of an Avalon-ST packet.

dout_ready

Input

dout

port Avalon-ST

ready

signal. The downstream

device asserts this signal when it is able to receive data.

dout_startofpacket

Output

dout

port Avalon-ST

startofpacket

signal. This signal

marks the start of an Avalon-ST packet.

dout_valid

Output

dout

port Avalon-ST

valid

signal. The IP core asserts this

signal when it produces data.

Table 17-4: Control Signals

Note: These signals are present only if you turn on Enable run-time control of input/output frame size and

turn off Bilinear for Scaling algorithm in the Scaler II parameter editor.

Signal

Direction

Description

control_address

Input

control

slave port Avalon-MM

address

bus. This bus

specifies a word offset in the Avalon-MM address space.

control_byteenable

Input

control

slave port Avalon-MM

byteenable

bus. This bus

enables specific byte lane or lanes during transfers. Each

bit in

byteenable

corresponds to a byte in

writedata

and

readdata

.

• During writes, this bus specifies which bytes are being

written to; other bytes are ignored by the slave.

• During reads, this bus indicates which bytes the master

is reading. Slaves that simply return

readdata

with no

side effects are free to ignore this bus during reads.

control_read

Output

control

slave port Avalon-MM

read

signal. When you

assert this signal, the

control

port sends new data at

readdata

.

control_readdata

Output

control

slave port Avalon-MM

control_data

bus. The

IP core uses these output lines for read transfers.

control_readdatavalid

Output

control

slave port Avalon-MM

readdata

bus. When you

assert this signal, the control port sends new data at

control_readdata

.

control_waitrequest

Output

control

slave port Avalon-MM

waitrequest

signal.

UG-VIPSUITE

2015.05.04

Scaler II Signals

17-13

Scaler II IP Core

Altera Corporation